「電源電圧の低電圧化」と「消費電流量の増加」は、主に高性能な半導体デバイス(CPU、GPU、FPGAなど)の進化に伴って発生する傾向であり、電力供給(パワーインテグリティ)において以下の深刻な課題を引き起こします。

1. 電力供給の安定性(電圧変動)の課題

電圧降下(IRドロップ)の影響増大

-

絶対的な電圧降下(V=IR): 供給電流(I)が増加するため、電源ラインの抵抗(R)による電圧降下(IRドロップ)が大きくなります。

-

相対的なマージンの縮小: コア電圧が低下している(例:5V→1.0V→0.7V)ため、同じ電圧降下量(例:0.1V)が発生した場合でも、相対的な電圧変動率が非常に大きくなります(例:5Vで2%だったものが、1Vで10%に)。

-

結果: LSIの動作マージンが狭くなり、わずかな電圧降下やノイズで誤動作や機能不良、あるいは性能低下(クロック周波数の維持困難)を引き起こすリスクが高まります。

過渡応答性の確保とノイズの増大

-

負荷の急激な変動: 高性能なLSIは、演算処理の瞬間に電流が急激に変動します(例:0Aから100Aへ)。

-

過渡応答の要求: 電源回路(DC-DCコンバータ)は、この急激な電流変動に対して、オーバーシュートやアンダーシュート(一時的な電圧の跳ね上がりや落ち込み)を許容範囲内(例:±5%以内)に収める高速な応答性が求められますが、従来の回路では困難です。

-

ノイズ(リップル・トランジェント): 大電流化に伴いスイッチング電源が多用されるため、高周波のリップルノイズや、負荷変動によるトランジェントノイズも大きくなり、これも誤動作の原因となります。

2. 熱・電力損失の課題

銅損(配線での損失)の増加

-

電力損失(P=I^2R): 電源ラインや基板配線の抵抗で消費される電力損失は、電流の二乗($I^2$)に比例します。電流が増えるほど、配線での電力損失が飛躍的に増大し、電源効率の低下を招きます。

-

発熱: 配線抵抗での損失は熱となり、LSIチップ自体の発熱と相まって、システム全体の熱設計を非常に困難にします。

電源回路設計の困難化

-

高効率化の要求: 低電圧・大電流を供給する電源回路(DC-DCコンバータ)自体にも、高効率化と小型化が求められます。特に大電流対応の電源回路は、より高度な制御技術(例:デジタル制御)や、放射ノイズ(EMI)の抑制技術が必要となり、設計難易度が飛躍的に上昇しています。

3. その他の課題

-

製造ばらつきの影響: 極端な低電圧で動作する回路は、半導体プロセスにおけるトランジスタの特性ばらつきの影響を強く受けやすくなり、設計マージンがさらに失われ、歩留まりの低下につながる可能性があります。

-

多電源化とサイズの課題: 高性能LSIは、コア電圧、I/O電圧など、複数の電源電圧を必要とするため、必要な電源回路の数が増加します。これにより、プリント基板上の占有面積が増大し、小型化の妨げになります。

真の電源ノイズ観測のための正しいプローブ選択 ~パワーレールプローブ~ SIGLENT SAP4000P

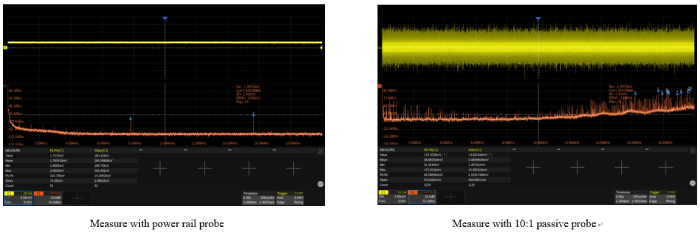

この動画は、通常のパッシブプローブとパワーレールプローブの違いを比較し、微小な電源ノイズ(リップル)を正確に観測するためにパワーレールプローブが必要であることを示しています。

|

|

|

|

|

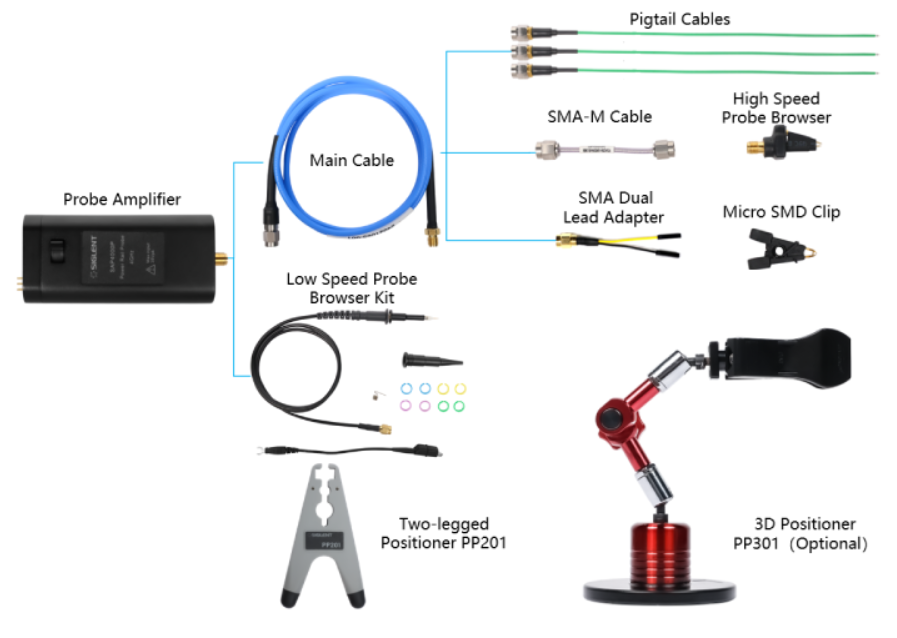

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

T&M

即納ストア

T&M

即納ストア