DDR2や一部のDDR3で主流だったT-ブランチ(Tree)トポロジと、現在のDDR4/5で標準的なFly-byトポロジの具体的な配線差について解説します。

最大の違いは、信号が各DRAMチップに「同時に届くことを目指すか」か「順番に届くことを許容するか」という設計思想にあります。

1. 配線構造の比較

T-ブランチトポロジ (DDR2/初期DDR3)

信号源(コントローラ)から1本のラインを引き、途中で対称に分岐させて各チップへ接続します。

-

等長配線の徹底: 全てのチップに信号が「全く同じタイミング」で届くよう、分岐後の配線長を厳密に揃えます。

-

スタブ(Stub)の問題: 分岐点からチップまでの配線が「切り株(スタブ)」となり、高速信号ではここで反射が起きて波形が乱れます。

-

物理的制約: チップ数が増えると分岐が複雑になり、基板上の配線スペースを圧迫します。

Fly-byトポロジ (DDR3/DDR4/DDR5)

信号源から最初のチップ、次のチップへと、1本のラインで「数珠つなぎ」に配線します。

-

最短スタブ: 分岐を作らず、メインの配線ラインのすぐ脇にチップを配置するため、反射を最小限に抑えられます。

-

終端の単純化: 配線の最終端に1つ終端抵抗を置くだけで、ライン全体のインピーダンス整合が取りやすくなります。

-

意図的な遅延: コントローラに近いチップと遠いチップで、物理的な到達時間に差(スキュー)が生じます。

2. 特性の違い(比較表)

| 項目 | T-ブランチ | Fly-by |

| 主な採用規格 | DDR2, 初期DDR3 | DDR3, DDR4, DDR5 |

| 信号の届き方 | 全チップ同時(同時刻) | 順番(時間差あり) |

| 反射ノイズ | 分岐部で発生しやすい | 極めて少ない |

| 設計の難易度 | 配線長の等長化が極めて困難 | スキュー補正(Write Leveling)が必要 |

| 対応クロック | 低~中速向き | 高速向き |

3. なぜDDR4はFly-byなのか?

DDR4以降のギガビット級の高速通信では、T-ブランチで生じる**「分岐による反射(波形の乱れ)」**が致命的になります。

そのため、ハードウェア(配線)側では反射を抑えるためにFly-byを採用し、そこで発生する「タイミングのズレ」については、メモリコントローラ側が各チップの距離を学習して信号送出をずらす**「Write Leveling(ライトレベリング)」**というデジタル処理で解決するアプローチに進化しました。

実装上の注意点

DDR4の設計では、アドレス/コマンド系はFly-byですが、データ系(DQ/DQS)は各チップとコントローラが1対1(Point-to-Point)で結ばれます。このため、「アドレス信号の遅延」と「データ信号の遅延」の整合性を考慮した配線設計が重要になります。

このあたりの、DQ/DQSとClockの配線長マッチング(パッケージ内遅延の考慮など)についても深掘りしますか?

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

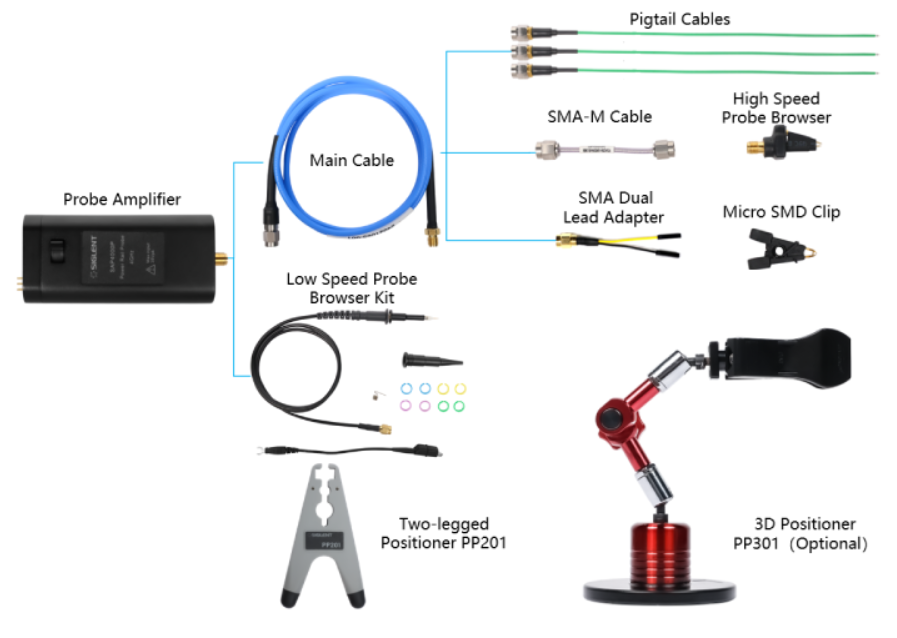

製品紹介:SIGLENT社 SAP4000P

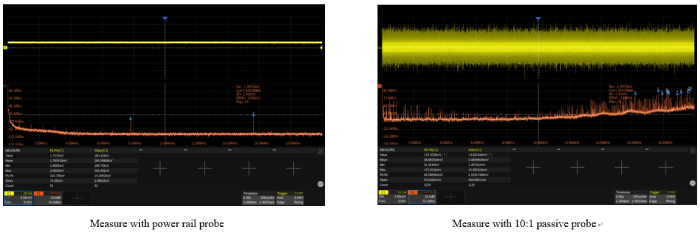

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア