FPGA(特にRFSoC)上で実装する**デジタル干渉キャンセラー(Digital Interference Canceller)**は、Wi-Fi 8などの強大な干渉波が存在する環境下で、微弱なWi-SUN FAN信号を抽出するための切り札となります。

4.5GHz帯のような広帯域かつ高密度な周波数利用を想定し、ロジック実装の具体的なアーキテクチャと最適化手法を詳述します。

1. アダプティブ・ノイズ・キャンセラー (ANC) の基本構造

FPGA上での干渉除去は、一般的にLMS(Least Mean Squares)アルゴリズムを用いた適応フィルタとして実装されます。

-

参照信号(Reference Signal): 干渉源(Wi-Fi 8など)の送信データ、または干渉波のみを捉えた別アンテナの入力を利用します。

-

誤差信号(Error Signal): 「混合信号(Wi-SUN + 干渉)」から「推定された干渉成分」を引き算した結果です。

-

更新ロジック: 誤差信号が最小になるように、フィルタ係数(Tap係数)をリアルタイムで更新し続けます。

2. FPGAロジックの実装ポイント

RFSoCの高速サンプリング環境では、1クロック内での処理が間に合わないため、パイプライン化と並列化が必須です。

① タップ係数の更新(Weight Update)

LMSの更新式 w(n+1) = w(n) + μ e(n) x*(n)$ を実装する際、ステップサイズ $\mu$ の調整が安定性の鍵です。

-

シフト演算への置き換え: μ を 2-n とすることで、重い乗算器を避け、バレルシッタ(位移演算)のみで実装し、DSPリソースを節約します。

② 複素演算の最適化

Wi-SUNのI/Q信号を扱うため、複素乗算器が必要です。

-

3乗算器構成: 通常の複素乗算(4乗算器)ではなく、代数的に変形した3乗算器構成をとることで、RFSoC内のDSP48E2スライス消費を25%削減できます。

③ 高速AXI-Streamインターフェース

ADCからのデータ(4.5GHz帯のDDC後データ)を滞りなく処理するため、TUSERなどのメタデータを用いてパケットの先頭(Start of Packet)を同期させ、干渉除去の収束タイミングを制御します。

3. Wi-Fi 8 等の広帯域干渉への対策:サブバンド分割

Wi-Fi 8のように帯域幅が非常に広い(最大320MHz)場合、単一のFIRフィルタではタップ数が膨大になり、FPGAのリソースを圧迫します。

-

Polyphase Filter Bank (PFB): まず信号を複数のサブバンドに分割します。

-

パラレル・キャンセル: 各サブバンドごとに独立した小型の干渉キャンセラーを並列配置します。

-

メリット: 各フィルタの動作周波数を下げつつ、広帯域な干渉を効率的に「削る」ことが可能です。

4. RFSoC SOM での実装レイアウト例

| モジュール | 実装場所 | 役割 |

| DDC (Hard IP) | RF-ADC内 | 4.5GHzからベースバンドへのダウンコンバート |

| Interference Estimator | FPGA (Programmable Logic) | 干渉波の振幅・位相をLMSで推定 |

| Subtraction Core | FPGA (Programmable Logic) | 混合信号から推定干渉波を減算(複素減算器) |

| hls4ml Equalizer | FPGA (Programmable Logic) | キャンセル後の残留ノイズを除去し、EVMを改善 |

5. デバッグと評価の自動化(PyVISAの活用)

実装したキャンセラーの効果を定量化するために、以下の環境を構築するのが効率的です。

-

信号生成: SG(信号発生器)でWi-Fi 8の干渉波を重畳させたWi-SUN信号を入力。

-

キャプチャ: RFSoCの内部信号(キャンセル前・後)をILA(Integrated Logic Analyzer)またはDMA経由で取得。

-

解析: Pythonで取得データを読み込み、EVM(Error Vector Magnitude)の変化をプロット。

-

「キャンセラーON/OFFでのBER(ビット誤り率)改善度」を自動計測するスクリプトを組むことで、最適なタップ数の選定が可能になります。

-

次のステップへのご提案

具体的に 「Vivado HLS で LMS フィルタを記述する際の DEPENDENCE プラグマの使い方」 や、「4.5GHz帯特有の位相雑音がキャンセラーの収束に与える影響の回避策」 について深掘りしましょうか?

あるいは、現在お使いの Avnet XRF シリーズ等のリソース状況(利用可能な DSP 数など)に合わせた設計最適化についてもアドバイス可能です。

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

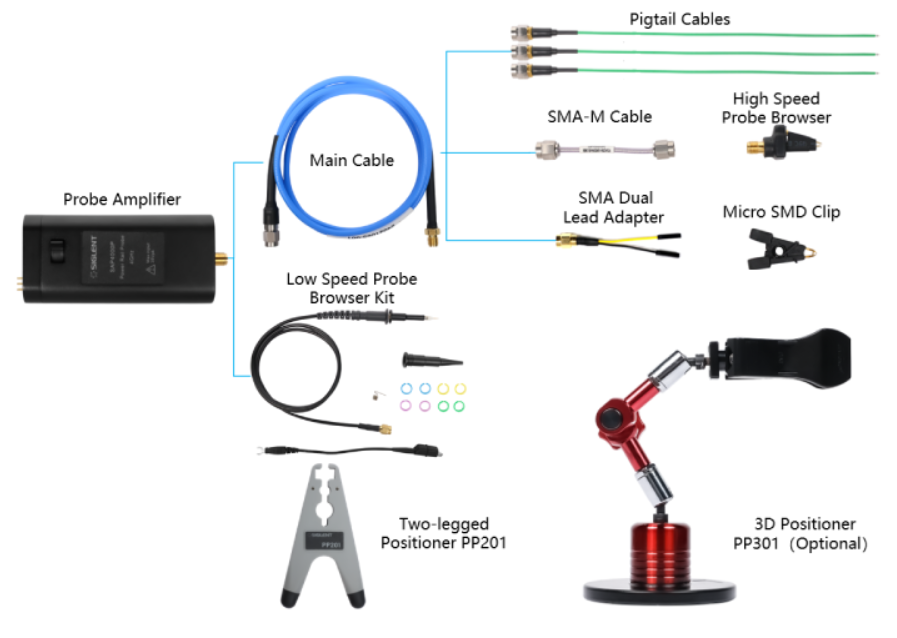

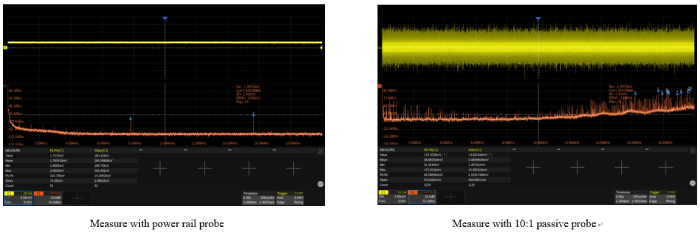

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア