「低電圧J級スタック型高効率増幅器」は、無線通信システムの送信機で求められる**「低電圧駆動」「高効率」「高出力」**という複数の要件を同時に満たすために、主に集積回路(IC)設計で用いられる高度な電力増幅器(PA)のトポロジーです。

この増幅器は、「J級動作」「スタック型構成」「低電圧技術」という3つの技術要素を組み合わせています。

🔬 1. J級(Class-J)動作

J級は、高効率増幅器の一つであるF級(Class-F)から派生した動作モードです。

-

原理: **高調波(二次、三次など)**の電流と電圧の波形を、出力整合回路によって適切に終端(コントロール)することで、トランジスタのドレイン(またはコレクタ)電圧と電流の波形が重なり合う時間を短縮し、電力損失を最小化します。

-

特徴: F級やE級に比べ、終端インピーダンスの設計に対する自由度が高く、広帯域にわたって高い電力効率を維持しやすいという利点があります。このため、「連続J級(Continuous Class-J)」として広帯域PAに利用されます。

🏗️ 2. スタック型(Stacked-FET)構成

スタック型構成は、低電圧駆動の集積回路プロセス(例:標準CMOSやSiGe BiCMOS)で高出力を得るために採用される技術です。

-

原理: 複数のトランジスタ(FET)を直列(スタック)に接続します。

-

効果:

-

高電圧対応: 各トランジスタにかかる電圧ストレスが分散され、個々のトランジスタは低耐圧プロセスで動作しつつ、出力端では高い電圧スイング(振幅)を実現できます。

-

高出力化: 結果として、低電圧プロセスでありながら、単一トランジスタ構造の数倍の出力電力を得ることができます。

-

広帯域整合: スタック構造は、出力インピーダンスを上げ、外部整合回路の設計を容易にする効果もあり、広帯域PAの設計に貢献します。

-

🤝 3. 低電圧 J級スタック型のシナジー

この複合トポロジーは、特に以下のような環境で大きな効果を発揮します。

-

CMOS/SiGe BiCMOSなどの低電圧プロセス: 低コストで大量生産が可能なこれらのプロセスで、携帯端末や小型基地局に必要な高出力PAを実現します。

-

高効率と広帯域の両立: J級の広帯域高効率特性と、スタック型の高電圧スイング能力を組み合わせることで、広帯域な信号(例:5G/6GのOFDM信号)を高効率かつ低歪みで増幅できます。

-

高集積化: 全てをICチップ上に集積するMMIC (Monolithic Microwave Integrated Circuit)の設計において、小型化と高性能化を両立させます。

この技術は、5G/6G通信システムにおけるモバイル端末や小型基地局のRFフロントエンドモジュールの鍵となる技術の一つです。

PR:

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

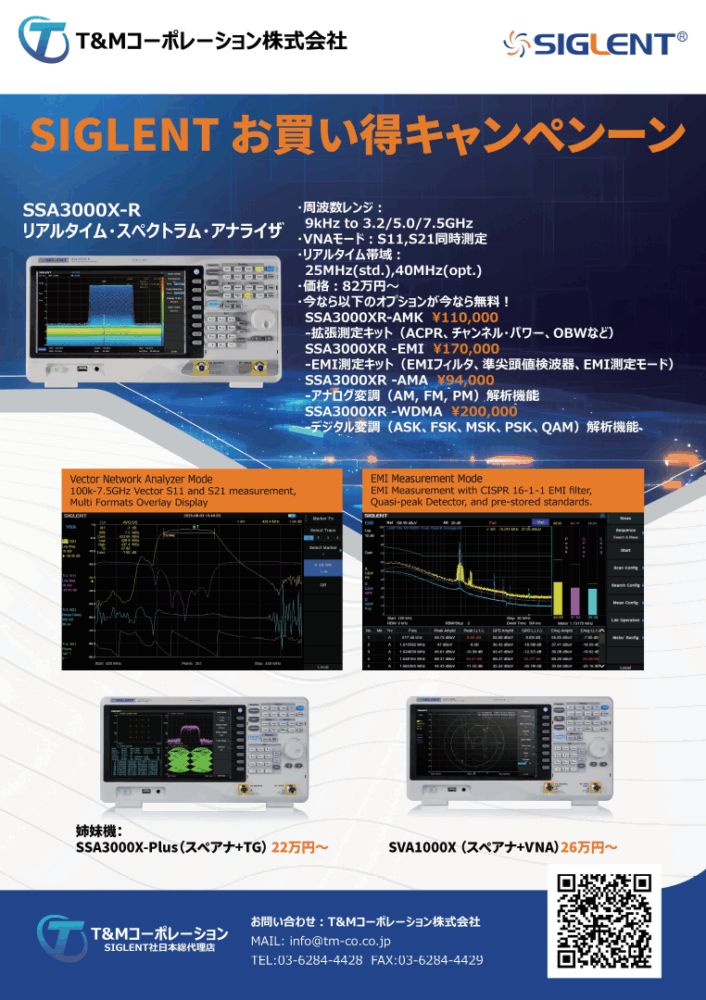

SIGLENT お買い得キャンペンーン実施中(~2026/03/31まで) SSA3000X-R シリーズ リアルタイム・スペクトラム・アナライザ (EMIフィルタ、準尖頭値検波器、EMI測定モード)

姉妹機も実施中(EMI測定機能は同じです) |

T&M

即納ストア

T&M

即納ストア