3次元構造を用いた先端光チップは、電子回路の限界を超えるための光電融合技術の究極形であり、複数のチップやデバイスを垂直方向に積層・統合することで、高性能、低消費電力、高密度な情報処理を実現します。

この技術は、主に**光集積回路(PIC: Photonic Integrated Circuit)と電子集積回路(CMOS IC)**の異種材料・異種機能集積に用いられます。

1. 3次元光チップの主要な構成技術 🏗️

先端光チップにおける3次元構造の実現には、複数の重要な技術が組み合わされています。

A. 3次元集積化技術 (3D Integration)

これは、半導体チップや光チップを垂直に積み重ね、高密度に相互接続する技術です。

-

ダイ・ツー・ウェハ接合 (Die-to-Wafer Bonding) または ウェハ・ツー・ウェハ接合 (Wafer-to-Wafer Stacking):

-

電子チップ(CMOS)と光チップ(SiフォトニクスやInP)を、極めて高い精度で貼り合わせます。

-

-

チップ貫通電極 (TSV: Through Silicon Via):

-

Siウェハを貫通して垂直方向に電気信号を伝達する配線です。これにより、上下のチップ間の配線長が劇的に短縮され、寄生容量や遅延が削減されます。

-

-

チップ貫通光インターコネクション (TSPV):

-

TSVの光版であり、チップ層間を光信号で接続する技術です。

-

B. 異種材料集積 (Heterogeneous Integration)

Siフォトニクス(Si基板)上に、発光体であるInPなどの化合物半導体を3次元的に統合し、Siでは困難な光源機能や光増幅機能をチップ内にもたらします。

2. 3次元光チップの利点 🚀

3次元構造は、従来の2次元的な光電集積では達成できなかった数多くのメリットを提供します。

-

超高密度化: チップを垂直に積層することで、面積あたりの機能密度が大幅に向上します。

-

低消費電力化:

-

電子回路と光回路、またはプロセッサとメモリ間の配線長が短縮されるため、信号伝送に伴う抵抗や容量が減少し、消費電力が劇的に低減します。

-

-

高性能化・低遅延化:

-

配線が短くなることで、信号伝送の遅延が最小化され、動作周波数の向上や大容量データ伝送が可能になります。

-

-

高機能化(複合機能):

-

異なる製造プロセスや材料で作られたチップ(例:CMOS、Siフォトニクス、InP光源)を最適に組み合わせることができ、単一のチップでは実現不可能な複雑で高性能なシステムを構築できます。

-

3. 応用分野

3次元光チップの技術は、以下のような分野で革新をもたらすと期待されています。

-

データセンター: Co-Packaged Optics (CPO)などの形で、CPU/GPUのすぐ近くに光トランシーバーを実装し、超高速・大容量のデータ通信を実現します。

-

AI計算基盤: 大量のAI演算チップとメモリを低遅延で接続し、処理能力とエネルギー効率を向上させます。

-

IOWN構想: NTTが目指すオールフォトニクス・ネットワークの実現に不可欠な、チップ内光配線への進化を可能にします。

この技術は、ムーアの法則に代わる集積回路のスケーリング技術として、半導体産業の未来を担う重要な要素です。

[未来の産業を担う三次元積層半導体(3D-IC)の現況と今後の展開―東北大学3D-IC研究開発拠点「GINTI」の活動成果より―] (https://www.youtube.com/watch?v=3zPtmCtSOJg)

この動画では、3次元積層半導体(3D-IC)のメリットと研究開発の現状が解説されており、先端光チップの集積化の基盤となる技術が理解できます。

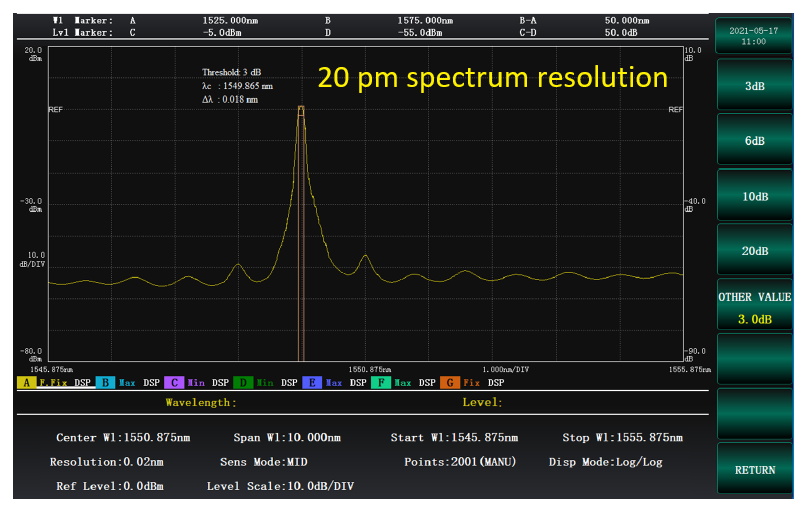

Ceyear社ではLightwave Component Analyzer、Optical Spectrum Analyzerをラインナップしています。

2025年マイクロウェーブ展ではLCA, 4port110GHzVNA(エクステンダーなし)など最新機器が展示されます。https://tm-co.co.jp/mwe2025/

T&M

即納ストア

T&M

即納ストア