「チップ・トゥ・ウエハー(Chip-to-Wafer: C2W)」のCu-Cuハイブリッドボンディングは、現在のAI半導体やHPC(高性能コンピューティング)の進化において、最も重要かつ難易度の高い実装技術の一つです。

従来の「ハンダバンプ」による接続を排し、銅(Cu)と絶縁膜(酸化膜など)の両方を同時に接合することで、端子間隔(ピッチ)を劇的に狭めることができます。

1. Cu-Cuハイブリッドボンディングの仕組み

この技術は、以下の2段階で接合が行われます。

-

絶縁層の接合(分子間結合): まず、平坦化された表面の絶縁膜(SiO2やSiCN)同士が室温で密着し、分子間力によって貼り合わされます。

-

金属の接合(原子拡散): 加熱(アニール)工程によって、絶縁層の中に埋め込まれた銅配線が熱膨張し、銅同士が接触。原子が拡散し合うことで強固な電気的・物理的接続が完成します。

2. 「チップ・トゥ・ウエハー (C2W)」である理由

ハイブリッドボンディングには「ウエハー・トゥ・ウエハー (W2W)」もありますが、現在の最先端チップにおいてC2Wが注目される理由は以下の通りです。

-

既知良品(KGD)の選別: 正常に動くチップ(Known Good Die)だけを選んでウエハーに載せられるため、歩留まり(良品率)が大幅に向上します。

-

異種チップの統合: サイズや製造プロセスが異なるチップ(例:TSMC製のロジックチップと他社製のメモリチップ)を組み合わせるヘテロジック集積に向いています。

-

柔軟な設計: W2Wのように上下のチップサイズを完全に合わせる必要がなく、設計の自由度が高いです。

3. C2Wハイブリッドボンディングの主要課題

非常に魅力的な技術ですが、量産化には高い壁があります。

-

極限の清浄度と平坦性: 表面にわずか数ナノメートルの塵があったり、CMP(化学機械研磨)後の凹凸が大きすぎたりすると、接合不良(ボイド)が発生します。

-

KGDの超高速・高精度配置: チップを1つずつ載せるため、W2Wに比べて生産性が低くなります。これを補うため、サブミクロン精度(±0.5μm以下)で高速にチップを配置できる「フリップチップボンダー」の進化が必須です。

-

プラズマ活性化: 接合強度を高めるため、貼り合わせ直前に表面をプラズマ処理して活性化させる高度な工程管理が求められます。

4. 業界の動向

-

TSMC (SoIC): TSMCの3Dパッケージング技術「SoIC」の主力技術として採用されています。AMDの「3D V-Cache」などが代表的な採用例です。

-

Intel (Foveros Direct): Intelは「Foveros Direct」という名称でハイブリッドボンディングを推進しており、ピッチを10μm以下まで微細化することを目指しています。

-

HBM (高帯域幅メモリ): 次世代のHBM4などでは、積層数増加に伴う厚みの制限をクリアするため、従来のハンダ接続からハイブリッドボンディングへの移行が議論されています。

出典:Google Gemini

PR:

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon

|

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

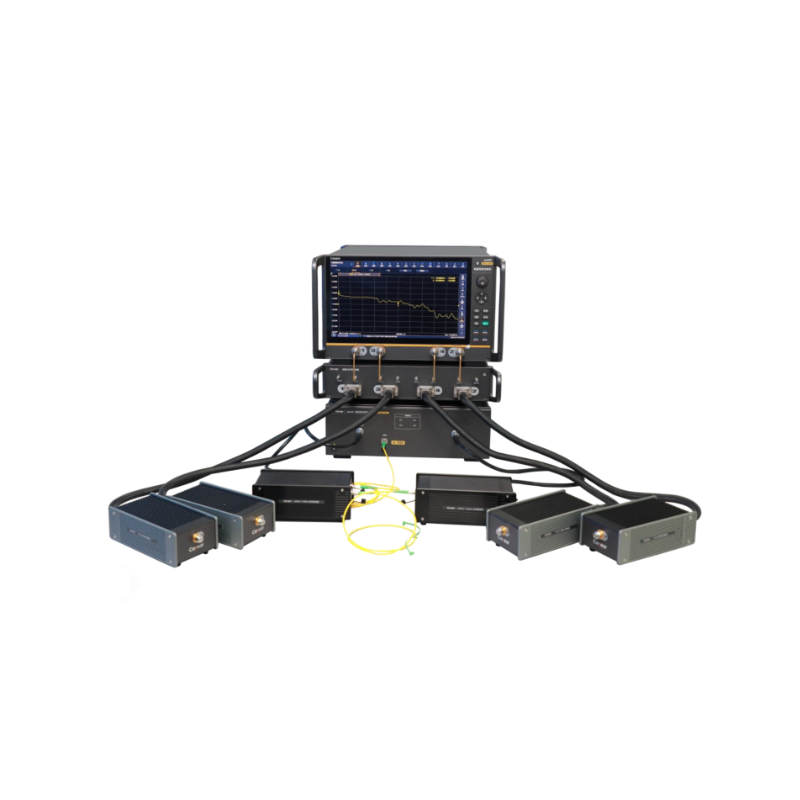

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年弱ですが着実に業績を伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転、スペースも拡大いたしました。

有名ブランドメーカーが値上げをする中、(110GHz VNAでは1億円超え)

弊社では若干の値下げをさせていただきました。(110GHz VNA、Ceyear社製は5000万円以下です。)

弊社、取扱メーカー各社は電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器にお客様のご予算を最大限生かす製品をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア