DDR4メモリ設計において、Fly-by(フライバイ)トポロジは信号の品質を保ち、高速なデータ転送を実現するための重要な配線手法です。

以前のDDR2などで採用されていた「T-ブランチ(木構造)」とは異なり、信号ラインを1本のパスで直列につなぐようなイメージです。

1. Fly-byトポロジの仕組み

Fly-byトポロジでは、**コマンド(Command)、アドレス(Address)、コントロール(Control)、クロック(Clock)**の信号が、メモリコントローラから各DRAMチップへと順番に(数珠つなぎに)伝わっていきます。

-

配線の単純化: 信号線が分岐しないため、インピーダンスの不整合による反射ノイズを劇的に抑えられます。

-

終端処理: 信号ラインの最後にのみ終端抵抗(VTT)を配置すればよいため、基板設計がシンプルになります。

2. メリットと課題

| 特徴 | 内容 |

| 信号品質 (SI) | 反射が少ないため、DDR4のような高クロック動作でも波形が崩れにくい。 |

| 基板設計 | 分岐配線(スタブ)を極限まで短くできるため、配線密度を高められる。 |

| 課題: 歪み (Skew) | 信号が物理的に「遠い」チップへ届くまでに時間がかかるため、チップ間で到達時間に差が出る。 |

3. 「Write Leveling」による補正

Fly-byトポロジの最大の弱点は、コントローラに近いチップと遠いチップで、信号が届くタイミングがズレること(フライトタイム・スキュー)です。

これを解決するために、DDR4には**Write Leveling(ライトレベリング)**という機能が備わっています。メモリコントローラが各DRAMチップに対して、クロック信号とデータ信号の位相差を検出し、あえて送信タイミングをずらすことで、全チップが同期して動作するように調整します。

まとめ

Fly-byトポロジは、**「反射ノイズを抑えるために直列配線を選び、その代償として生じる遅延のズレをデジタル技術(Write Leveling)でカバーする」**という、非常に合理的な設計手法です。

このトポロジの対比として語られることが多い「T-ブランチトポロジ」との具体的な配線差についても詳しく解説しましょうか?

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

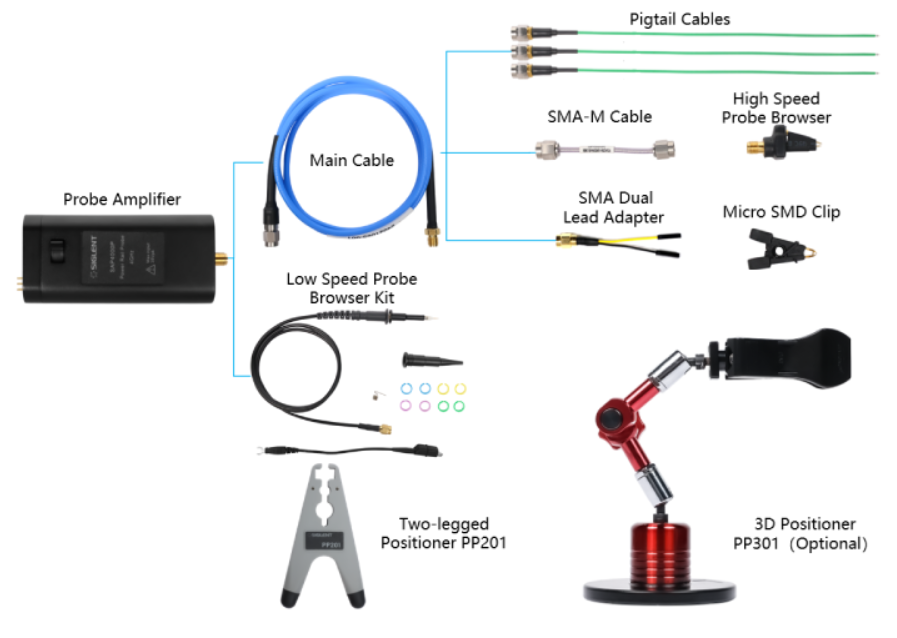

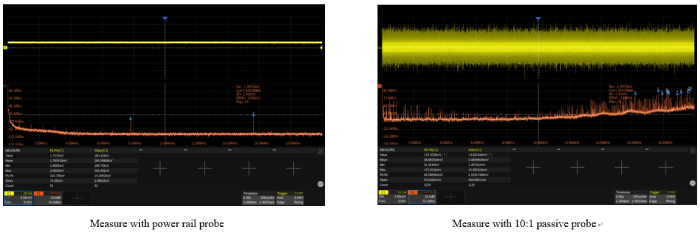

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア