FPGAを用いたOFDM復調回路の最適化、特にWi-SUN FAN 1.1(最大2.4 Mbps / 920MHz帯)や、RFSoC SOM(4.5GHz評価系)のような環境を想定した実装では、「スループットの確保」と「演算リソース(DSP/LUT)の削減」、そして**「レイテンシ(処理遅延)の極小化」**のトレードオフをどう管理するかが鍵となります。

以下に、主要な最適化手法を4つのレイヤーで整理します。

1. FFT/IFFTコアのパイプライン化とスケーリング

OFDMの心臓部であるFFT処理の最適化です。

-

ストリーミング・アーキテクチャ: XilinxのFFT IP等を使用する場合、

Pipelined Streamingモードを選択し、ADCからのデータを止めることなく連続処理します。これにより、シンボル間のガードインターバル(GI)処理との同期が容易になります。 -

ビット幅の動的スケーリング: 固定小数点演算における精度落ち(量子化雑音)を防ぐため、バタフライ演算ごとにスケーリングを行う「Block Floating Point」を検討してください。

-

リソース共有: 複数チャネルを同時に復調する場合、FFTコアを時分割で共有するか、あるいはRFSoCの豊富なDSPを活用して並列配置するかを、利用可能なLUT/DSPの残量に応じて決定します。

2. 位相同期(Carrier Phase Recovery)の高速化

マルチホップ環境や高周波帯では、周波数オフセットや位相雑音が無視できません。

-

CORDICアルゴリズムの活用: 乗算器(DSP)を節約するため、ベクトル回転や位相角の計算にはCORDIC(Coordinate Digital Computer)回路をパイプライン実装します。

-

パイロット信号によるシンボル内補正: OFDMシンボル内に埋め込まれたパイロット信号を用いて、FPGA上でリアルタイムに位相回転を補正します。ここをハードウェア化することで、CPU(Arm)側でのソフト処理待ちによる遅延を排除できます。

3. hls4mlを用いた「チャネル等化器(Equalizer)」の最適化

前述の通信路推定(Channel Estimation)をhls4mlで実装する場合の具体的最適化です。

-

AP_FIXEDの最適化: ```cpp

// 符号1bit, 整数部4bit, 小数部12bitの例

typedef ap_fixed<16, 4> model_default_t;

このようにビット幅を絞ることで、DSPを消費せずLUTのみで構成される「ロジックベースの積和演算」を増やせます。 -

並列度の調整(Unrolling): hls4mlの

Reuse Factorを1に設定すると、すべてのニューロンが独立した回路として展開され、最小レイテンシ(クロック数サイクル)で推論が完了します。RFSoCの高速クロック(300MHz〜500MHz程度)であれば、OFDMの1シンボル時間内に余裕を持って収まります。

4. RFSoC SOM特有の「デジタル遅延」への対策

Avnet XRFシリーズなどのSOMを使用し、4.5GHz帯デバイスを評価する場合、以下の物理的な制約が回路設計に影響します。

-

群遅延の補償: RFフロントエンドやADC内のデジタルフィルタによる群遅延を考慮し、時間領域でのシンボル同期(Packet Detection)の閾値や窓関数(Windowing)のタイミングを微調整する必要があります。

-

AXI-Streamのバックプレッシャー管理: FPGA内の復調データがArm側のDDRメモリへ転送される際、バスの混雑によるデータ欠落を防ぐため、十分な深さのFIFO(First-In First-Out)バッファを配置し、クリティカルな復調処理が停止しないように設計します。

最適化によるリソース/性能の比較(目安)

| 手法 | リソース (DSP/LUT) | レイテンシ | 精度 (EVM) |

| 標準的なIP + CPU処理 | 低 | 高 (msオーダー) | 中 |

| FPGA純粋ハードウェア化 | 中 | 低 (μsオーダー) | 高 |

| hls4mlによるML最適化 | 高 (設定による) | 極低 (ns-μs) | 最高 |

次のステップへのご提案

具体的な実装において、**「Vivado HLSでの具体的なコード記述(pragma)」や、「4.5GHz帯での信号劣化を想定した学習データの収集方法」**について、さらに詳細な情報を生成しましょうか?あるいは、RFSoCのADC設定に関する技術的なご質問などがあればお聞かせください。

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

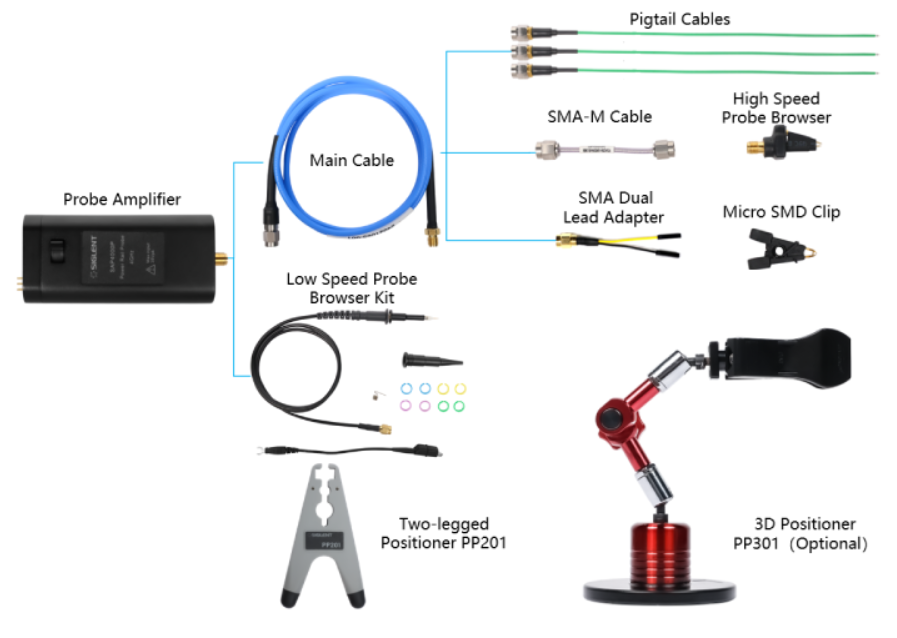

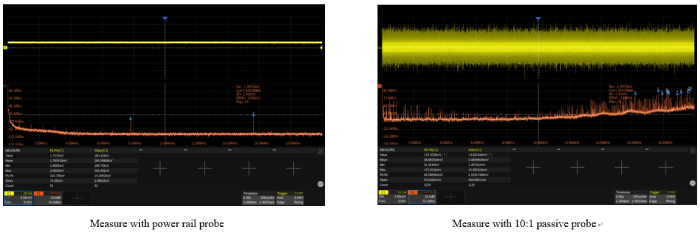

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア