2026年現在、PyTorchやTensorFlowで学習したモデルを、ドローン中継のような超低遅延環境(ターゲット:サブミリ秒)で動かすには、hls4mlを用いたFPGAへのハードウェア実装がデファクトスタンダードとなっています。

各アーキテクチャ(RNN, CNN, LSTM等)をRFSoCへ実装する際の、具体的な遅延対策と2026年時点の最新動向をまとめます。

1. アーキテクチャ別の低遅延化戦略

モデルの種類によって、FPGA上でのボトルネックと対策が異なります。

-

CNN(畳み込みニューラルネットワーク):

-

対策: ストリーミングI/Oとラインバッファの活用。

-

詳細: 映像の1フレーム全体を待つのではなく、数ライン(行)読み込んだ時点で畳み込み演算を開始します。RFSoCのAXI4-Streamインターフェースと直結することで、メモリ転送待ちを排除した「オンザフライ」の処理が可能です。

-

-

RNN / LSTM(再帰型ニューラルネットワーク):

-

対策: フィードバックパスのハードウェア最適化。

-

詳細: RNN/LSTMは前の時刻の状態(Hidden State)を次へ渡す必要があるため、逐次処理が遅延の元になります。hls4mlの最新バージョン(v1.3.x以上)では、再帰部分をパイプライン化し、サンプリングレートに同期させた並列演算が強化されています。

-

2. 2026年版:hls4mlによる最適化ワークフロー

最新のツール環境では、以下の機能が低遅延化を支えています。

-

QONNXとHGQ(High Granularity Quantization):

-

従来の均一な量子化ではなく、層ごと、あるいは重みごとに最適なビット幅(1bit〜8bit)を自動選択するHGQ2が実用化されています。これにより、4.5GHz帯の評価で重要な「精度(EVM)」を維持しつつ、回路規模とレイテンシを最小化できます。

-

-

Vitis HLS 2024.1以降との親和性:

-

AMD(Xilinx)の最新コンパイラ最適化により、RFSoCのDSP58スライス(Versal世代に準ずる高効率演算器)を最大限に叩き出し、演算レイテンシを数クロック単位で削減します。

-

3. 実装のトレードオフ:Reuse Factorの制御

hls4mlで最も重要なパラメータが Reuse Factor です。

-

Reuse Factor = 1: 完全に並列化(Unrolled)。リソースを最大に使いますが、レイテンシは最小(1クロックで1レイヤー通過等)になります。

-

Reuse Factor > 1: 回路を再利用。リソースを節約しますが、時分割処理になるためレイテンシが増加します。

-

推奨: ドローン中継用ノイズ除去であれば、特定の重要レイヤー(入力層に近いCNNやLSTMのゲート演算)のみ

Reuse Factor = 1に設定し、残りを調整する「ハイブリッド構成」が有効です。

4. RFSoC SOM(XRFシリーズ)での実運用

SOM上での1.8V電源品質(±3%)を考慮すると、以下の設計が推奨されます。

-

デジタル・アイソレーション: AI推論エンジンの急激なスイッチングがADCのサンプリング精度に干渉しないよう、FPGA内の配置配線(Floorplanning)で、RFデータコンバータ付近のロジック使用を意図的に避ける設計が必要です。

-

確定的応答の検証: シミュレーション段階で、ADCのサンプリングからAI処理を経てDAC/無線出力に至るまでの「絶対遅延時間」が一定(Deterministic)であることを確認してください。

具体的な実装に向けて、さらに深掘りしたい技術情報はありますか?

たとえば、「hls4mlでPyTorchのモデルを変換する際の具体的な設定ファイルの書き方」や、「RF-ADCからのストリーミングデータを直接AI IPに入力するためのインターフェース設計」など、より実践的なアドバイスも可能です。

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

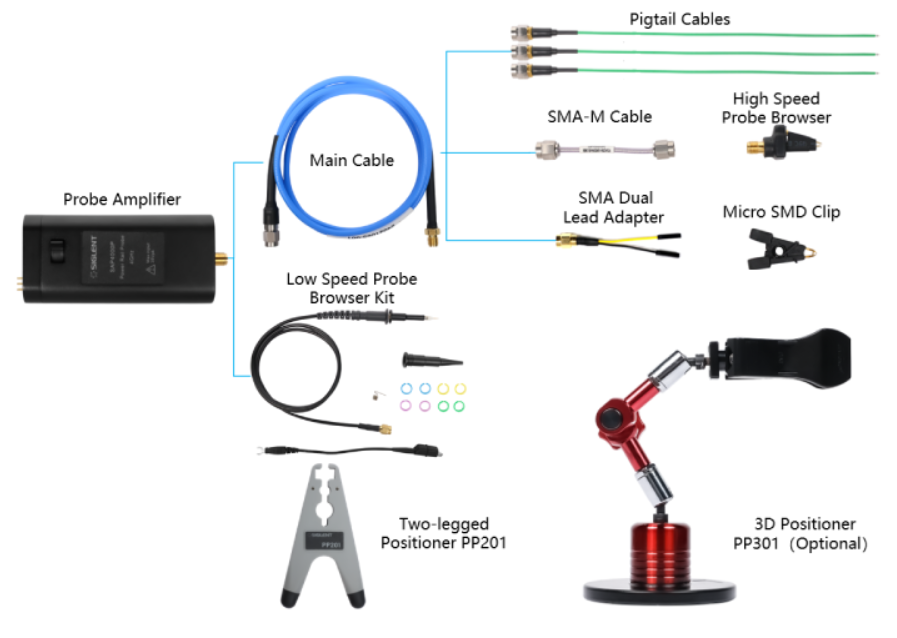

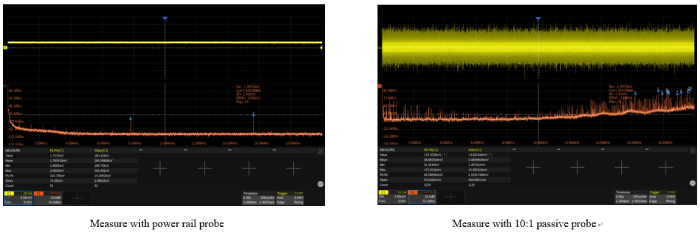

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア