RFSoC(Zynq UltraScale+ RFSoCなど)を用いた4.5GHz帯デバイスの評価において、DDC(Digital Down Converter)のチャネル設計は、後段のFPGAロジック(Wi-SUN FAN 1.1の復調器やhls4ml推論コア)に「いかにクリーンで扱いやすい信号を渡すか」を決定する極めて重要な工程です。

特に、広帯域なADC入力を、Wi-SUNのような比較的狭帯域(数十kHz〜数MHz)な信号へ効率的に落とし込むための設計ポイントを整理します。

1. ミキシング・プロトコルとNCO設定

4.5GHzの入力を処理する場合、RFSoCのADCサンプリングレート(例:4.096 GSa/sや5.0 GSa/s)に基づいたナイキスト・ゾーンの選択が必要です。

-

ダイレクト・サンプリング: 第2または第3ナイキスト・ゾーンを利用して4.5GHzを直接取り込む場合、**NCO(Numerically Controlled Oscillator)**をマイナスの周波数に設定し、ベースバンド(0Hz近傍)へデジタル的にシフトさせます。

-

位相雑音の抑制: NCOの設定分解能(通常48bitなど非常に高精度)を活かし、中心周波数のオフセットを最小限に抑えます。これは、Wi-SUN FAN 1.1で導入されたOFDMのサブキャリア間隔(数kHz〜数十kHz)の同期精度に直結します。

2. デシメーション(Decimation)によるS/N比の向上

ADCの高速サンプリングレートから、Wi-SUNのシンボルレートに適した低速レートへ変換する過程で、**処理利得(Process Gain)**を得ることができます。

-

多段構成の活用: RFSoC内部のハードウェアIPである「Decimation Filter(例:x2, x4, x8...)」を組み合わせます。

-

例:4GSa/s → (x8) → 500MSa/s → (x100 FPGA側) → 5MSa/s

-

-

オーバーサンプリング効果: デシメーションにより帯域外ノイズが抑制され、実効ビット数(ENOB)が向上します。これにより、微弱なWi-SUN信号の検出感度が改善されます。

3. I/Q不平衡の補正とフラットネス

4.5GHz帯のような高周波では、アナログ・フロントエンドやADCの特性により、IチャネルとQチャネルの間でわずかな利得差や位相差(I/Q Imbalance)が生じやすくなります。

-

デジタル補正: RFSoCのDDC内にある複素ミキサーとデジタルフィルタを利用し、通過帯域内のフラットネスを確保します。

-

群遅延の管理: 4.5GHz帯のデバイス評価において、変換アダプタ等の物理的要因による遅延を含め、DDC内のデジタルフィルタによる群遅延を把握しておく必要があります。これは、FPGA側で実装するシンボル同期のタイミング判定(Matched Filter)に影響します。

4. マルチチャネル設計(Wi-SUN FANの同時待ち受け)

RFSoCの強力な機能の一つが、1つのADC入力に対して複数のDDCを並列に走らせる「Multi-Band/Multi-Channel」構成です。

-

独立したNCO/Decimator: 異なるチャネル(周波数)で動作するWi-SUNノードを、同時にデジタル・ダウン・コンバートし、個別のAXI-StreamとしてFPGAロジックへ流し込めます。

-

リソース効率: DDCはハードウェアIPとしてADCに内蔵されているため、FPGAのロジック(LUT/DSP)を消費せずに、複数のWi-SUNチャネルをリアルタイムで分離・抽出可能です。

チャネル設計のパラメータ例(イメージ)

| パラメータ | 設定値の考え方 | 理由 |

| ADC Sampling Rate | 4.096 GSa/s | システムクロックとの整数比を維持 |

| NCO Frequency | -4.500 GHz (等) | ターゲット信号をベースバンドへシフト |

| Decimation Ratio | x8 or x16 | 後段のFPGA処理負荷の低減とS/N向上 |

| Output Format | IQ (Complex) | 直交復調および等化処理のため |

実装に向けた次のステップ

Avnet XRFシリーズなどのSOMを使用されている場合、**RF Analyzer(GUIツール)**を用いて、まずは4.5GHzの入力信号が正しくDDCを通過し、FFT結果としてベースバンドで観測できるかを確認するのが第一歩です。

その際、**「デジタル領域でのフィルタ設計(Vitis Model Composerなど)」や、「AXI-StreamのデータレートとFPGAクロックの同期」**について、具体的なトラブルシューティングや設計手法を深掘りしますか?

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

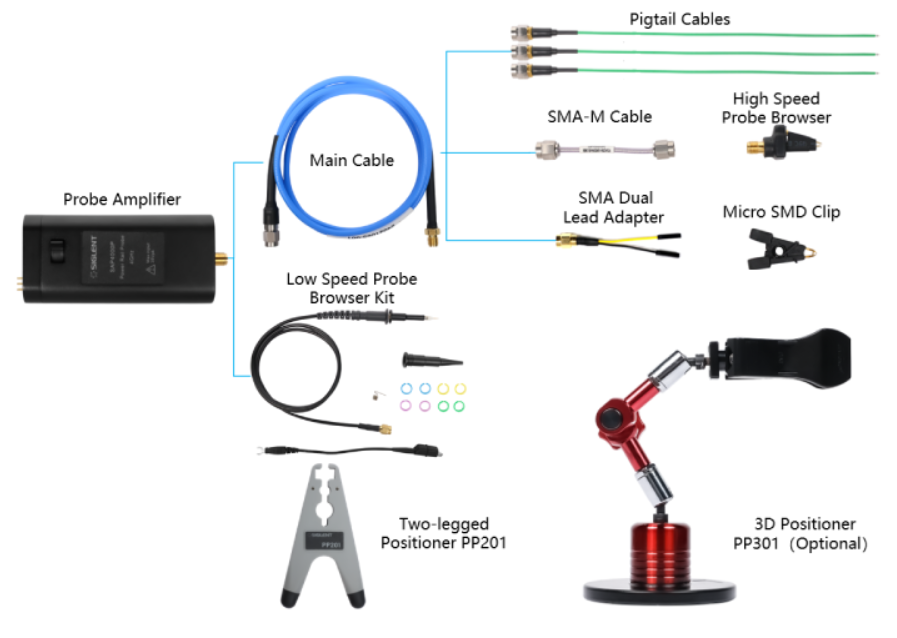

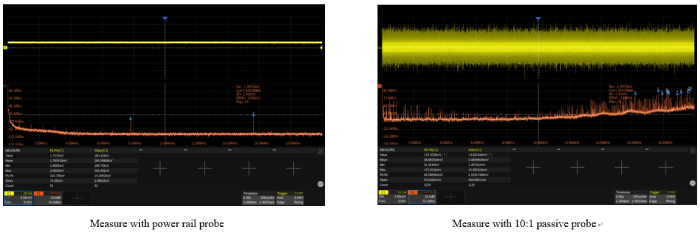

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア