ウエハー上のCD1.6μmの3層RDL形成は、再配線層 (RDL: Redistribution Layer) を用いた次世代半導体パッケージング技術における微細化の進展を示すものです。

特に、CD1.6μmという非常に微細な線幅で3層のRDLを形成する技術は、高密度な配線が要求されるファンアウト・ウェハーレベル・パッケージング (FoWLP) や2.5D/3D集積などの先端パッケージングで重要となります。

💡 RDLと微細化の重要性

-

RDL (再配線層):

-

半導体チップの入出力端子 (I/O) の配置を再構成し、チップ上の回路をパッケージの外部接続端子 (バンプなど) まで電気的に接続するための配線層です。

-

複数のRDL層を積層することで、より複雑な配線ルーティングと高密度の接続が可能になります。

-

-

CD1.6μm (Critical Dimension 1.6マイクロメートル):

-

配線パターンの最小加工寸法(線幅や線間隔)が1.6マイクロメートルであることを示します。これは非常に微細であり、従来のパッケージング技術では困難なレベルです。

-

この微細化により、配線密度が向上し、チップ間の高速信号伝送や省スペース化、高性能化が実現します。

-

-

3層RDL:

-

3つの配線層と、それらを接続するビア(層間接続)層から構成されます。層数が増えるほど、配線経路の自由度が増し、より多くのチップや複雑な機能の集積が可能になります。

-

🔍 実現技術の例

このCD1.6μm、3層RDLの形成は、特にダマシン法 (Damascene Process) を用いたRDL形成技術の進展として注目されています。

-

ダマシン法:

-

従来のポリマーを誘電体として用いる方法(ポリマー法)よりも微細な配線の形成に適しています。

-

絶縁膜(誘電体)に溝(配線パターン)や穴(ビア)を形成した後、Cuなどの金属を埋め込み、余分な金属を化学的機械的研磨 (CMP) で除去して配線を形成します。

-

このレベルの微細化は、AIチップやHBM (High Bandwidth Memory) といった高性能デバイスを統合する次世代の半導体パッケージングにおいて、不可欠な技術とされています。

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

|

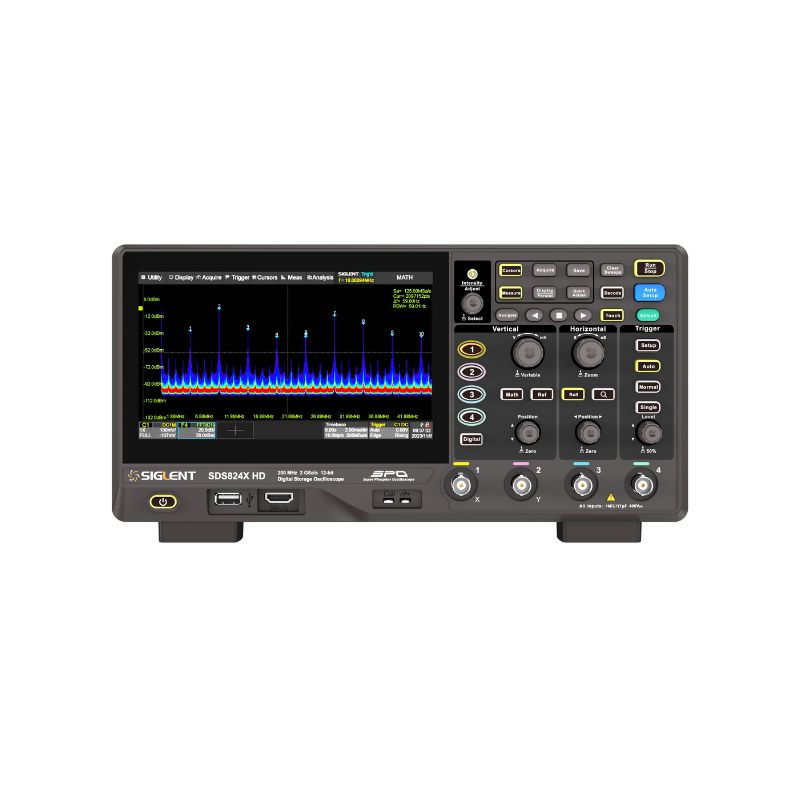

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

T&M

即納ストア

T&M

即納ストア