デジタルICのトーテム・ポール出力段におけるEMC(電磁両立性)対策について

トーテム・ポール出力段は、HighとLowのいずれかの状態が確定するため、信号レベルが不安定になることがないという利点があります。しかし、この出力段が状態を切り替える際に、一瞬だけ上下のトランジスタが両方ともオンになる瞬間があります。この短い時間、電源レールがグラウンドに短絡されたような状態になり、大きな過渡電流が流れます。これは「貫通電流」と呼ばれ、EMC対策上重要な課題となります。

この貫通電流と、それが電源レールに引き起こす電圧ノイズは、電磁妨害(エミッション)の主な原因となります。以下に、これらの問題に対する一般的なEMC対策をいくつか挙げます。

1. デカップリングコンデンサの適切な配置

-

ICの電源ピンとグラウンドピンの間に、できるだけ近い位置にデカップリングコンデンサを配置します。

-

このコンデンサは、ICのスイッチング時に発生するノイズ電流を吸収し、電源ラインへのノイズ放射を低減する役割を果たします。

-

貫通電流によるノイズは高周波成分を多く含むため、高周波特性の良い積層セラミックコンデンサを使用することが推奨されます。

2. グラウンドプレーンの活用

-

プリント基板(PCB)の設計において、広範囲なグラウンドプレーンを設けることで、ノイズの低減に効果があります。

-

グラウンドプレーンは、ノイズ電流のリターンパスを短くし、インダクタンスを低減する効果があります。

3. スルーレートの制御

-

トーテム・ポール出力のスイッチング速度(スルーレート)が速いと、貫通電流のピーク値が大きくなり、ノイズも増大します。

-

回路の必要要件を満たす範囲で、スルーレートを意図的に遅くするよう設計することで、ノイズを抑制できる場合があります。

-

ただし、スルーレートを遅くしすぎると、信号の伝送速度に影響が出るため、トレードオフの関係になります。

4. 適切なICの選択

-

ICのEMC性能が不明な場合は、複数の競合製品を実際にテストしてみることが重要です。

-

特に、クロックを使用した動作や、高データレートでの動作など、実際の使用環境に近い条件でエミッション試験を行うことで、ICのEMC特性を評価できます。

-

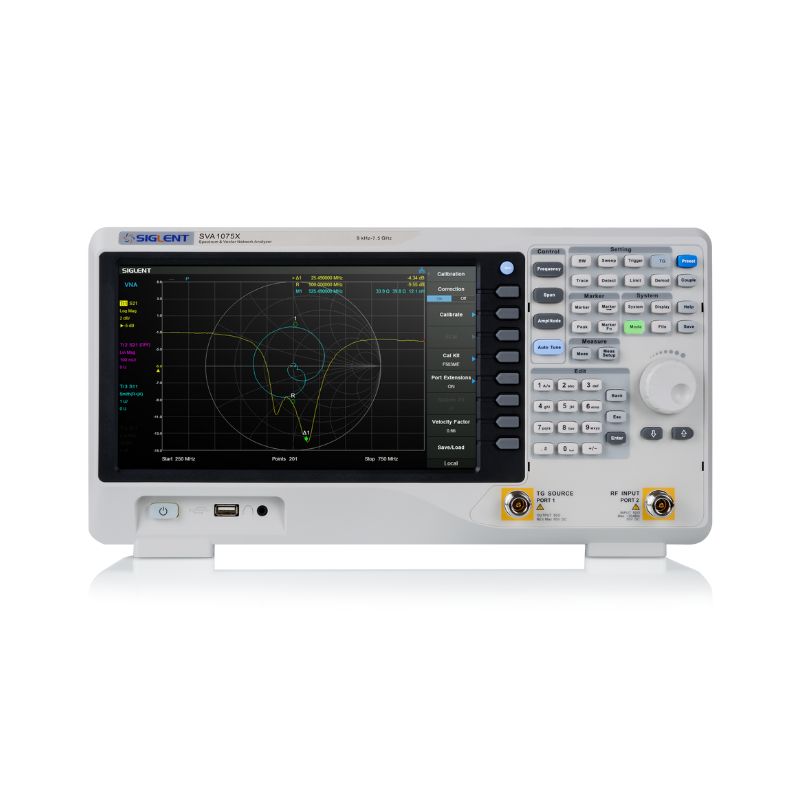

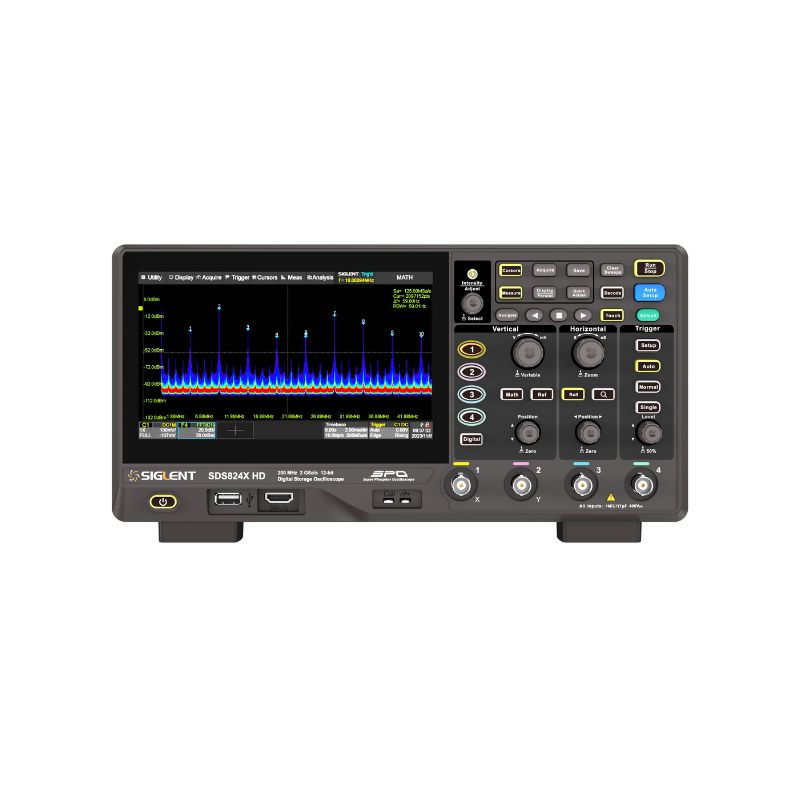

スペクトラムアナライザや高帯域オシロスコープと近接磁界プローブを使用すれば、比較的簡単にエミッションの評価が可能です。

5. フィルタリング

-

電源ラインや信号ラインに、ノイズ除去のためのフィルタを挿入することも有効です。

-

コモンモードチョークコイルやフェライトビーズなどを利用して、ノイズを抑制します。

これらの対策は、設計の初期段階から考慮することで、EMCの問題を未然に防ぐことができます。

T&M

即納ストア

T&M

即納ストア