0.5Vのような**超低電圧(Ultra-Low Voltage: ULV)**でアナログRF(Radio Frequency)回路を設計することは、IoT、ウェアラブルデバイス、生体医療インプラントなどの分野で極めて重要な技術です。これは、バッテリー駆動時間の延長やエネルギーハーベスティングによる電源動作を可能にするためです。

しかし、0.5VでのRF回路設計は、従来の設計手法では解決できない多くの深刻な課題を伴います。

🚨 0.5V RF回路設計の主な課題

1. ヘッドルームの不足 (Headroom Constraint)

0.5Vという電源電圧は、CMOSトランジスタの通常の動作に必要な電圧範囲(電圧ヘッドルーム)を著しく制約します。

-

しきい値電圧(VT)の問題: 標準的なCMOSプロセスにおけるVT(通常、0.3V〜0.5V程度)が電源電圧に近いため、トランジスタを飽和領域(定電流源として機能する領域)で動作させることが困難になります。特に、直列に接続できるトランジスタの数が1個に限定されるため、カスコード構造などの高性能な回路トポロジーが使用できなくなります。

-

信号振幅(スイング)の制約: 許容される信号の最大振幅が電源電圧(0.5V)によって制限されます。これにより、**ダイナミックレンジ(DR)**が大幅に劣化し、ノイズ耐性が低下します。

2. スイッチングの問題(RFスイッチ)

RF回路ではしばしばスイッチングが使用されますが、低い電源電圧ではスイッチのオン抵抗を十分に下げることが困難になります。

-

トランジスタのゲート電圧が低いため、RF信号を効率的に通過させることが難しくなります。

3. トランジスタ特性の変動

VTに近い電圧で動作させるため、トランジスタの動作が非線形になりやすく、プロセス、電圧、温度(PVT)変動に対する**ロバスト性(堅牢性)**が低下します。

-

VTのわずかな変動が回路性能に大きな影響を与えます。

-

RF回路で重要な**ノイズ特性(1/fノイズなど)やミスマッチ(デバイス間のばらつき)**の影響が顕著になります。

⚙️ 0.5V RF回路を実現する主要な設計技術

これらの課題を克服するため、0.5V(またはそれ以下)の電源電圧で動作するアナログRF回路設計には、特殊な技術が用いられます。

1. サブスレッショルド/ウィークインバージョン動作

トランジスタをしきい値電圧以下のサブスレッショルド領域で動作させる手法です。

-

利点: この領域では、トランジスタは指数関数的に小さな電流で動作するため、極めて低い消費電力を実現できます。

-

課題: 動作速度が遅くなり、非線形性やノイズが増加する傾向があります。RF回路では速度が必要なため、適用は難しい場合がありますが、バイアス回路や低速な制御回路では有効です。

2. バルク駆動技術 (Body/Bulk Driving)

MOSFETのゲートではなく、バルク(基板)端子を信号入力として利用する手法です。

-

利点: ゲートに比べてバルク端子の駆動電圧範囲は小さくて済むため、低電圧電源でもトランジスタを飽和領域近くで動作させやすくなります。

-

課題: バルク端子の入力抵抗が低く、寄生容量が大きいため、RFのような高周波信号を扱うのには向かない場合が多いですが、低周波のアナログブロックでは広く使われています。

3. 電圧/電流再利用(Voltage/Current Reuse)

一つの電流パスや電圧ノードを複数の機能ブロックで共有することで、必要な電圧降下や電流消費を抑える手法です。

-

例: LNA(低ノイズアンプ)とミキサを縦に積まず、並列に配置したり、共通の電流源を共有したりすることで、回路全体の$V_\text{DD}$を低く保ちます。

4. トランジスタの特性変更/最適化

設計時にVTが低いトランジスタ(LVT: LowVT)を選択したり、トランジスタのサイズ(W/L)を最適化したりすることで、低電圧での性能を向上させます。

これらの技術を組み合わせ、主にLNA(低ノイズアンプ)やVCO(電圧制御発振器)、ミキサなどの重要なRFフロントエンド回路を0.5Vで実現する研究が精力的に進められています。

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

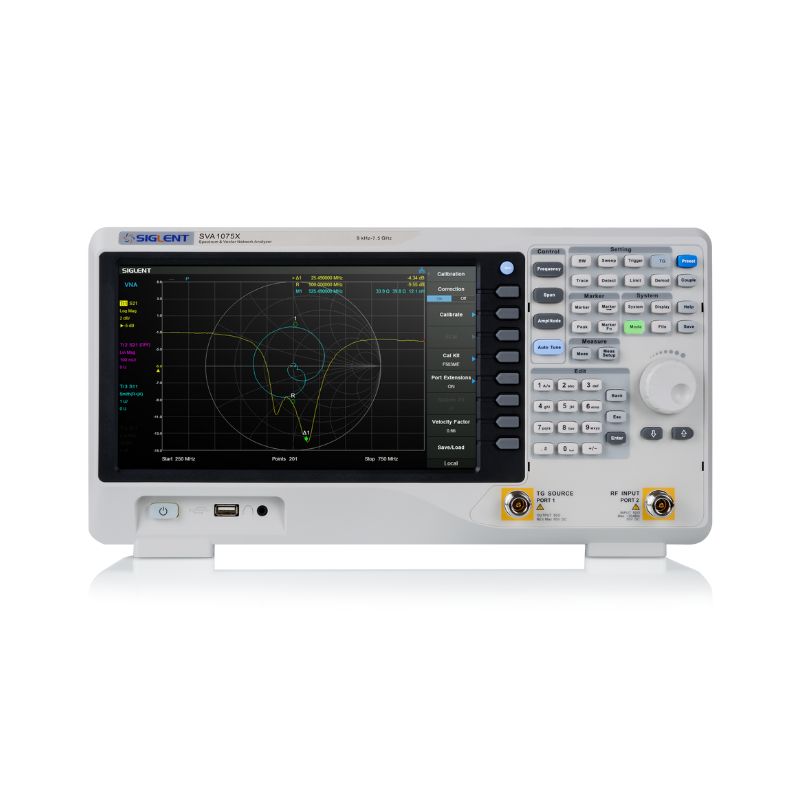

SNA6000A Series Vector Network Analyzer Key Features

|

T&M

即納ストア

T&M

即納ストア