AIモデルをFPGAやLSI(ASIC)へ実装する際、最大の壁は**「限られたハードウェア資源(メモリと演算器)」と「リアルタイム性(超低レイテンシ)」**の両立です。無線通信の歪み補正(DPoD/DPD)ではナノ秒〜マイクロ秒単位の処理が求められるため、以下の計算削減テクニックが不可欠となります。

1. 量子化(Quantization)

浮動小数点(FP32)の演算を、精度の劣化を抑えつつ固定小数点(INT8, INT4など)に変換します。

-

メリット: FPGA上のDSP(デジタル信号処理)ブロックの使用を抑え、ルックアップテーブル(LUT)での演算を可能にします。

-

混合精度(Mixed-Precision): 重要な重みには8ビット、それ以外には4ビットを割り当てるなど、層ごとにビット幅を最適化する手法です。

2. 構造化プルーニング(Structured Pruning)

ニューラルネットワーク内の「重要度の低い接続(重み)」や「チャネル」を削除してモデルを軽量化します。

-

非構造化 vs 構造化: * 非構造化: 個別の重みをゼロにする(FPGAでは回路が疎になり、逆に実装効率が落ちることがある)。

-

構造化: チャネルやフィルタごと削除する(行列演算のサイズそのものが小さくなるため、ハードウェア実装と相性が非常に良い)。

-

-

効果: 演算量とメモリ帯域の両方を削減し、推論の高速化に直結します。

3. 回路レベルの最適化

ハードウェアの特性を活かしたアルゴリズムの工夫です。

-

ルックアップテーブル(LUT)との融合:

AIモデルの一部を、事前に計算した値を格納したメモリ(LUT)に置き換えます。例えば、活性化関数の計算や複雑な非線形項をLUT化することで、演算器を節約します。

-

ストリーミング・パイプライン処理:

各層の計算を直列に並べ、信号が流れる間に次々と計算を完了させる手法です。これにより、バッファメモリを最小限に抑えつつ、通信のスループットを維持します。

-

Winogradアルゴリズム / FFTの活用:

畳み込み演算(CNN)を、行列積よりも計算効率の良い数学的空間へ変換して実行します。

4. DPoD特有の軽量化手法

通信ドメイン特有の知識(Domain-Specific Knowledge)を用いた削減技術も重要です。

| テクニック | 内容 |

| 実数変換(RVNN) | 複素数演算をそのまま行うのではなく、I信号とQ信号を実数として処理する専用アーキテクチャで、複素乗算の数を1/4程度に削減。 |

| デルタ推論 | 時間的に近いサンプルは変化が少ないため、前の推論結果との「差分」だけを更新し、全レイヤーの再計算を避ける。 |

| 時間的疎性(Temporal Sparsity) | 信号の振幅が小さい(歪みが少ない)区間では、AIの計算精度や動作頻度を動的に落として消費電力を抑える。 |

実装に向けた最新ツールチェーン

現在では、Pythonで書いたPyTorch/TensorFlowモデルを自動でFPGA用のHDL(ハードウェア記述言語)に変換するツールも進化しています。

-

AMD (Xilinx) Vitis AI: 最適化からFPGA実装までの一貫したフローを提供。

-

hls4ml: 高エネルギー物理学などの超低レイテンシ用途向けに、ニューラルネットワークをHLS(高位合成)コードに変換するオープンソース。

次にお手伝いできることはありますか?

「特定のFPGA(ZynqやAgilexなど)でのベンチマーク結果」や、「hls4mlを用いた具体的な実装フロー」について詳しく知りたい場合は、ぜひ教えてください。

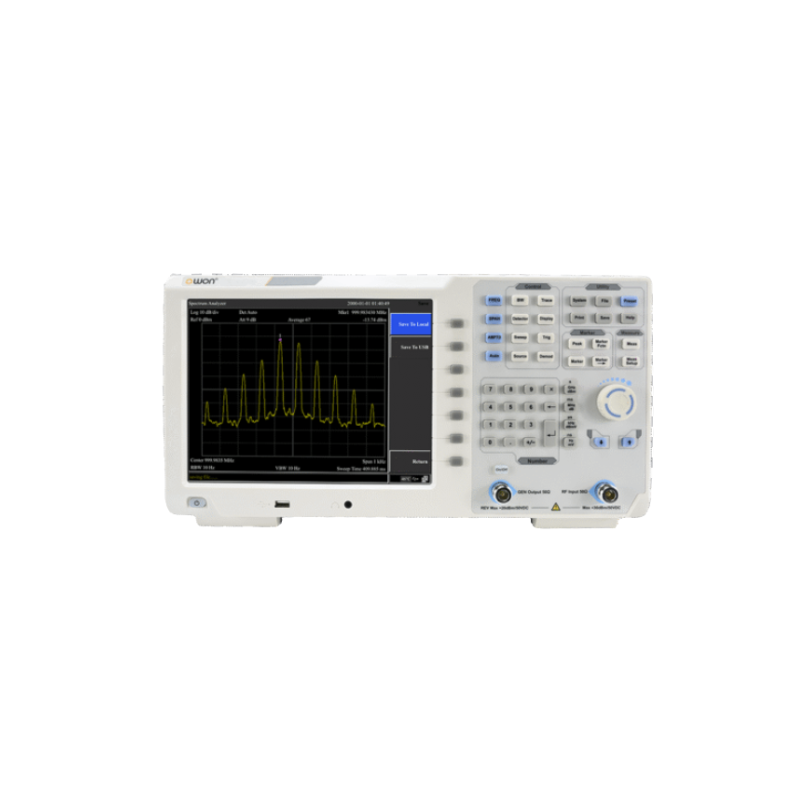

T&M

即納ストア

T&M

即納ストア