AMD(Xilinx)のFPGAでTSNを実装する場合、主に 「TSN Endpoint Ethernet MAC」 というIPコアを使用します。この設定は、VivadoのIP CatalogからカスタマイズGUIを開いて行いますが、28Gbpsクラスの高速通信やLPDDR4の帯域設計と整合させるための重要なチェックポイントがいくつかあります。

1. Vivado IPコンフィギュレーションの主要項目

VivadoのGUI上で設定する際、特に「Qbv(スケジューリング)」に関連する項目は以下の通りです。

① General Tab(基本設定)

-

Endpoint Type: 1G / 2.5G / 10G(またはそれ以上)を選択します。

-

Interface Selection: 通常、内部バスは AXI4-Stream を使用します。LPDDR4からDMA(Direct Memory Access)経由でデータを流し込む際のメインパイプラインとなります。

-

Number of Queues: 802.1Qbvで制御する優先度キューの数を指定します(最大8)。

② TSN Features Tab(機能有効化)

-

Time-Aware Shaper (802.1Qbv): ここをチェックすることで、GCL(Gate Control List)のハードウェア・ロジックが有効になります。

-

Precision Time Protocol (802.1AS): 時刻同期機能を有効にします。GCLはこのPTP時刻と完全に同期して動作します。

2. GCL(Gate Control List)の初期値埋め込み

VivadoのGUI上、またはIPの生成後に「GCLプログラミング用インターフェース」を介して設定します。

-

Static Configuration: IPのプロパティ設定で、テキスト形式または16進数のリストとしてGCLエントリを記述します。

-

例:

0x01_0000C350(ゲート1のみ開放、期間50,000ns)

-

-

Dynamic Configuration (AXI-Lite): 運用中に設定を変更する場合、FPGA内部のプロセッサ(Cortex-A53等)から AXI-Lite バス経由でIP内部のレジスタ(GCL RAM)を書き換えます。

3. LPDDR4帯域とFIFOしきい値の調整

28Gbps/56Gbps I/Oで取り込んだデータをTSNで送出する際、Vivadoの設定で最も注意すべきは 「バッファサイズ(FIFO)」 です。

-

TX/RX FIFO Depth: GCLによって「送信ゲートが閉じている時間」が長い場合、その間にLPDDR4から読み出されたデータがIP内部のFIFOに溜まります。

-

計算:

(ゲート閉時間) × (AXIバスの供給レート)以上の容量を確保しないと、バス側でバックプレッシャー(転送停止)がかかり、LPDDR4の読み出し効率が低下します。

-

-

PFC (Priority-based Flow Control): 必要に応じて802.1Qbb(PFC)を有効にし、バッファ溢れを防ぐフィードバック制御を組み込みます。

4. デバッグツールの活用

設定したGCLが正しく動作しているかは、Vivadoの ILA (Integrated Logic Analyzer) で波形を観測するのが確実です。

-

観測ポイント:

-

tx_gate_open_status: 各キューのゲートが開いているかを示す信号。 -

ptp_time_counter: ナノ秒単位の時刻カウンタ。 -

これらを並べて表示し、意図した Time Interval(例えば50,000ns)で信号が変化しているかを実機確認します。

-

次のステップへの提案

実際にVivadoでプロジェクトを構成される際、**「LPDDR4からTSN IPへデータを運ぶためのDMA(AXI DataMover等)の最適なバースト長設定」**について詳しく知りたいですか?

あるいは、IBERTで確認した高速リンクの「安定性」が、PTPの同期外れ(Sync Loss)を引き起こしていないかを判定する、ハードウェア・ステータスレジスタの監視方法について解説が必要でしょうか?

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

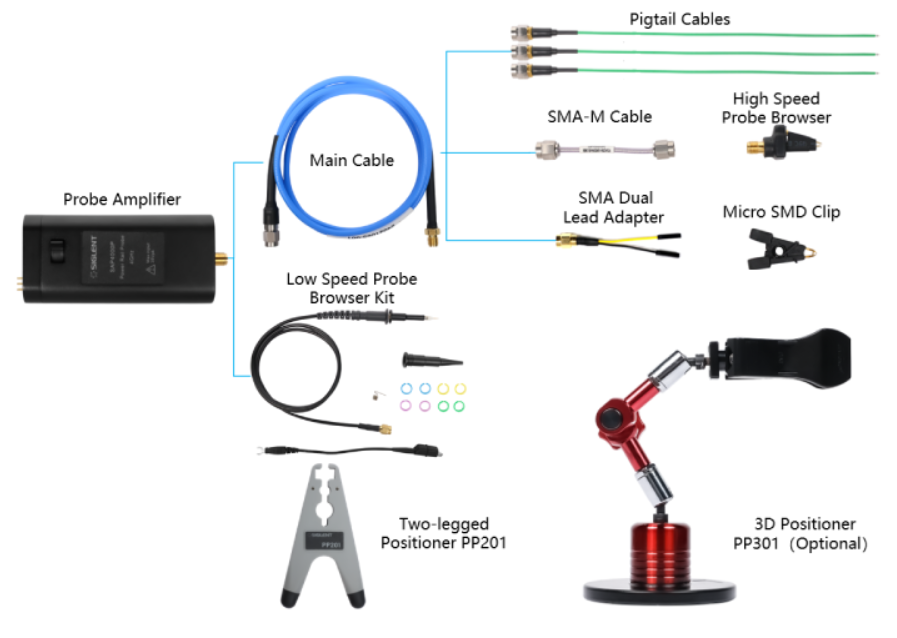

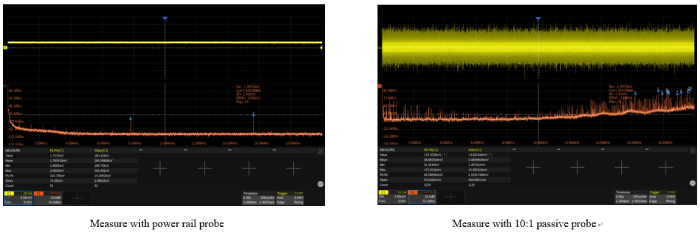

製品紹介:SIGLENT社 SAP4000P

パワーインテグリティ測定用シグレント・パワーレールプローブSAP4000P

SAP4000P パワーレール・プローブ, 4 GHz, オフセット電圧範囲:±24 V, ¥880,000

|

|

|

|

|

https://tm-co.co.jp/SAP4000P_UserManual

PR:

|

・USB VNA |

・Coming soon |

|

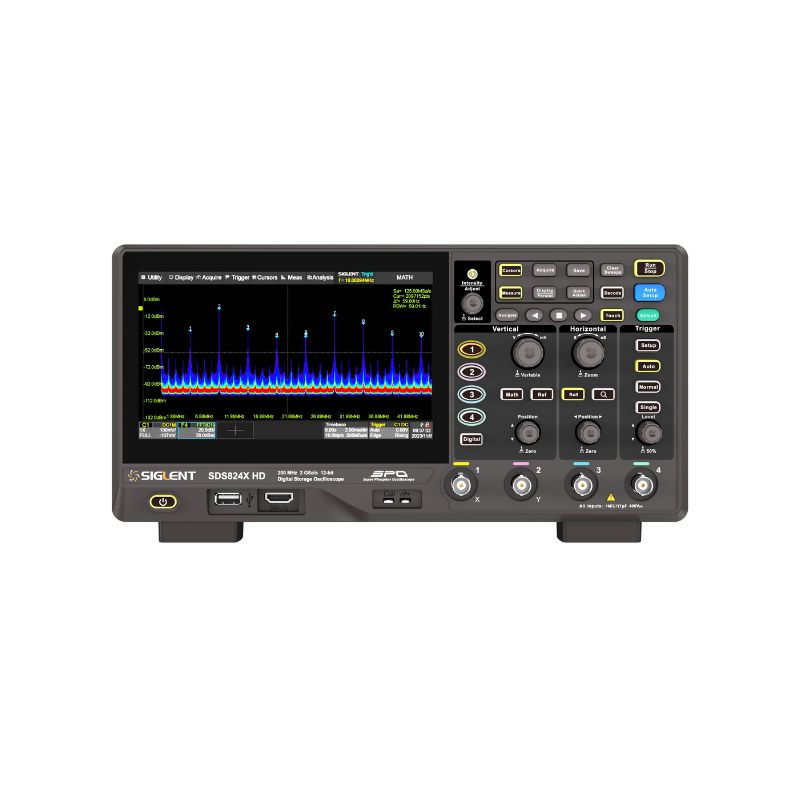

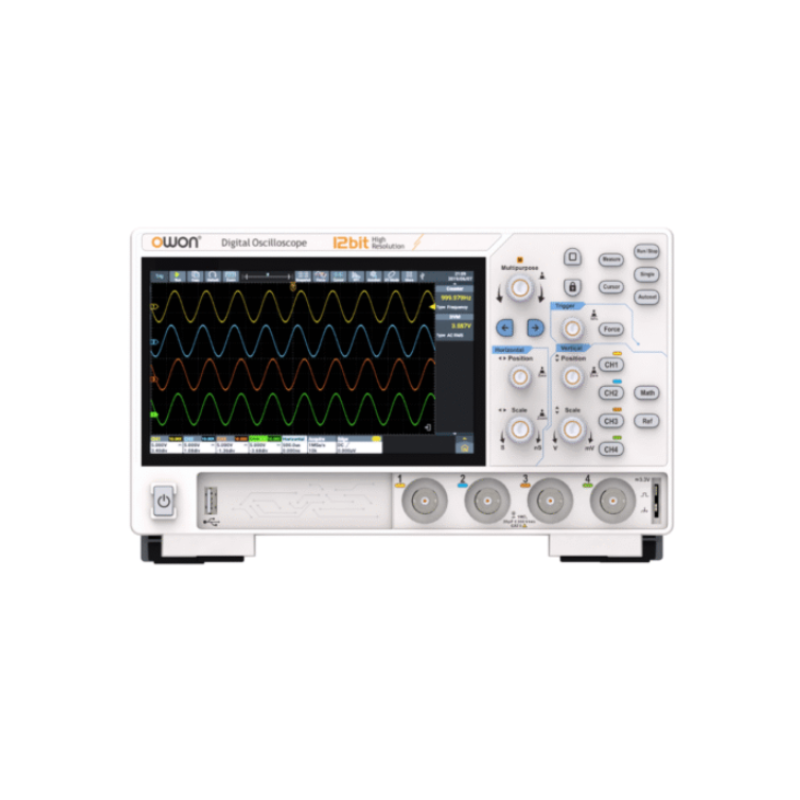

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア