PCIe 6.0 の 64 GT/s という数字は、単なるスピードアップ以上の技術的限界への挑戦を意味しています。

高周波信号を扱う上で、この「64 GT/s」がどのようなインパクトを持つのか、エンジニアリングの視点から主要なポイントを整理します。

1. 物理的な伝送限界との戦い

PCIe 5.0(32 GT/s)までは NRZ 方式でしたが、64 GT/s に到達するために PAM4 を採用した最大の理由は、ナイキスト周波数を抑えるためです。

-

周波数特性: 64 GT/s を NRZ で実現しようとすると 32 GHz の帯域が必要になりますが、PAM4 なら 16 GHz(PCIe 5.0 と同等)で済みます。これにより、一般的な PCB 基材(FR-4 など)やコネクタでの信号減衰(インサーションロス)を、従来の設計の延長線上で制御可能にしています。

-

アイ・クロージャ: PAM4 は電圧振幅を 3 分割するため、1 つの「アイ」の高さは NRZ の 3 分の 1 になります。S/N 比が約 9.5 dB 悪化するため、より精密なイコライゼーション(CTLE/DFE)と VNA を用いた厳密なデエンベディング技術が不可欠です。

2. 64 GT/s における実効スループット

PCIe 6.0 では、128b/130b エンコーディングから FLIT モード へ移行したことで、オーバーヘッドの計算が変わりました。

-

x16構成の帯域: $64 \text{ GT/s} \times 16 \text{ lanes} \div 8 \text{ bits/byte} = 128 \text{ GB/s}$(片方向)

-

双方向合計: 最大 256 GB/s

-

実効効率: FLIT(256バイト固定)を採用することで、従来のエンコーディングによる 1.5% 程度の損失がなくなり、プロトコル上の効率はほぼ 100% に近くなっています。ただし、FEC(誤り訂正)や CRC のための冗長ビットが FLIT 内に含まれます。

3. レイテンシへの影響

「FEC を使うと遅延が増えるのでは?」という懸念に対し、PCIe 6.0 は非常に巧妙な設計をしています。

-

低レイテンシ FEC: 64 GT/s という超高速域では、強力すぎる FEC は演算時間を要し、レイテンシを悪化させます。そのため、PCIe 6.0 では「数ナノ秒」レベルで処理可能な軽量 FEC を採用しています。

-

リトライとの併用: 軽量 FEC で直しきれないバーストエラーが発生したときのみ、リンク層でのリトライ(再送)を行います。これにより、平均的なレイテンシを PCIe 5.0 と同等レベルに抑えています。

開発・検証における留意点

この速度域になると、ボード設計における 1.8V 以下の低電圧レールにおける電源インテグリティ(PI) や、変換アダプタ(N-SMA 等)による反射の影響が極めて顕著になります。

特に、4.5 GHz 付近の評価を行っている場合、その高調波成分(3次:13.5 GHz、5次:22.5 GHz)が PCIe 6.0 のナイキスト周波数近傍に位置するため、クロストークや不要放射の管理がよりシビアになります。

出典:Google Gemini (Gemini は AI であり、間違えることがあります。)

PR:

SMM3000Xシリーズ 高精度ソースメジャーユニット・表示桁数:6½桁(2,100,000カウント) ・SMM3311X(1ch) / SMM3312X(2ch) ・価格:90万円~ |

|

|

・USB VNA |

・Coming soon |

|

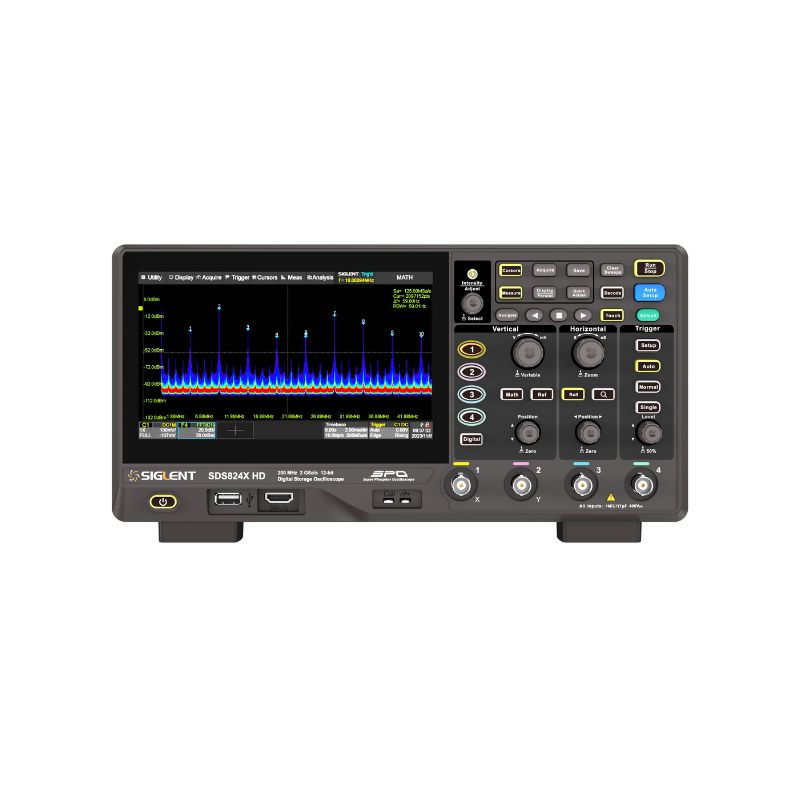

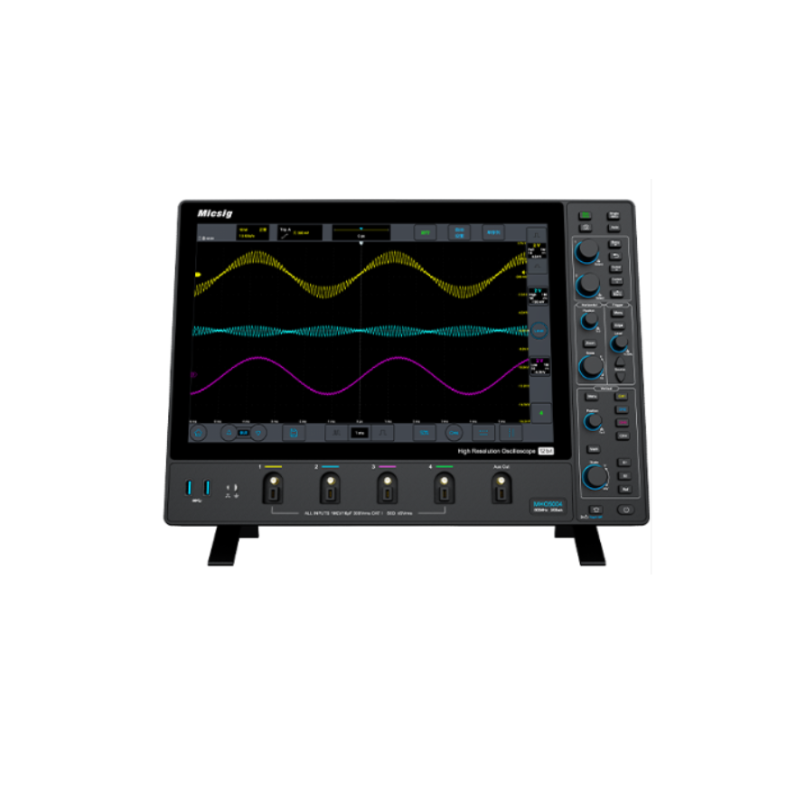

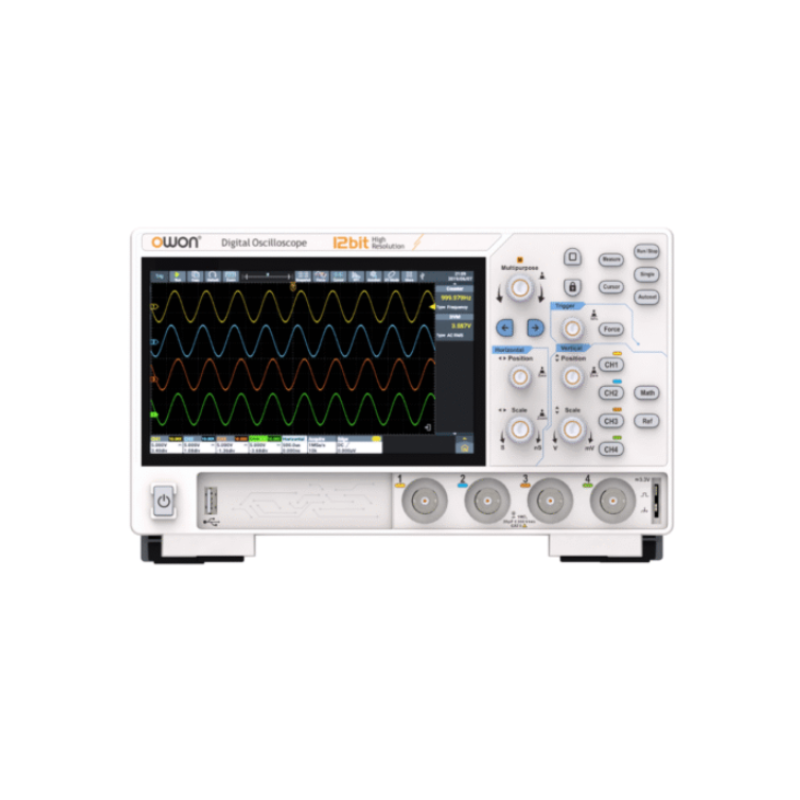

SDS8000Aシリーズ オシロスコープ 特長と利点 ・Coming soon |

|

SSG6M80Aシリーズ ・Coming soon

|

|

|

|

SSA6000A Series Signal Analyzer Main Features ・Coming soon

|

|

SNA6000A Series Vector Network Analyzer Key Features

|

お礼、

T&Mコーポレーションは設立5年ですが、おかげさまで業績を着実に伸ばしており、

オフィスを港区芝(最寄り駅浜松町)に移転し、スペースも拡大いたしました。

電子計測器業界の「ゲームチェンジャー」として、高性能/高信頼/低価格/短納期を武器に

T&Mコーポレーションはお客様のご予算を最大限生かす製品群をご提案させていただいております。

T&M

即納ストア

T&M

即納ストア