ロジックチップにおける3次元構造がもたらす利点は、主に微細化の限界突破とシステム全体の高性能化・高効率化の2点に集約されます。これは、トランジスタレベルの3次元構造(GAAFET、CFETなど)と、チップレベルの3次元積層(3D IC)の両方で効果を発揮します。

1. トランジスタレベルでの利点(チャネルの立体化)

FinFET、ナノシートFET(GAAFET)、CFETなどのトランジスタにおける3次元構造化は、主に微細化の限界を克服し、トランジスタの基本性能を向上させます。

| 構造 | 例 | 主な利点 |

| 全周ゲート | ナノシートFET (GAAFET) | ゲートがチャネルを四方から完全に囲むため、リーク電流を極限まで抑制し、オン/オフの切り替えをシャープにします(静電制御の向上)。 |

| チャネル積層 | CFET (Complementary FET) | NMOSとPMOSを垂直に積層することで、CMOS回路に必要な横方向の占有面積を約半分に縮小し、集積度を劇的に向上させます。 |

| 実効チャネル幅の増加 | FinFET、ナノシートFET | 設置面積(フットプリント)を大きくすることなく、チャネルを立体的にすることで実効的な駆動電流(オン電流)を増やし、動作速度を向上させます。 |

2. チップレベルでの利点(チップの垂直積層 - 3D IC)

異なる機能を持つ複数のチップ(ロジック、メモリなど)を垂直に積み重ねて接続する3次元積層技術(3D IC)は、システムレベルでの利点をもたらします。

✅ 性能の大幅な向上(高速化・低遅延)

-

配線長の短縮: 従来の2次元平面配置では、チップ間の通信は長い配線(I/O)を経由していました。3D積層では、TSV (Through Silicon Via: シリコン貫通ビア) という垂直な配線により、通信距離が劇的に短縮されます。

-

データ転送の高速化: 配線長が短くなることで、信号遅延が減り、超高速なデータ転送が可能になります。

✅ 電力効率の改善(低消費電力化)

-

消費電力の削減: 配線長が短くなると、信号を伝送するために必要な電力が減ります。これにより、システム全体の消費電力を大幅に抑えることができます。

-

低ノイズ化: 配線が短くなることで、ノイズの発生を抑え、信号品質が向上します。

✅ 高集積化と小型化

-

フットプリントの削減: 複数のチップを縦に重ねるため、横方向の占有面積(フットプリント)を減らし、パッケージの小型化・高密度化を実現できます。

-

異種統合の容易化: 異なるプロセスで製造された機能(ロジック、高性能メモリ、RF、センサーなど)を、最適な状態で個別に製造し、後から統合することが容易になります(ヘテロジニアスインテグレーション)。

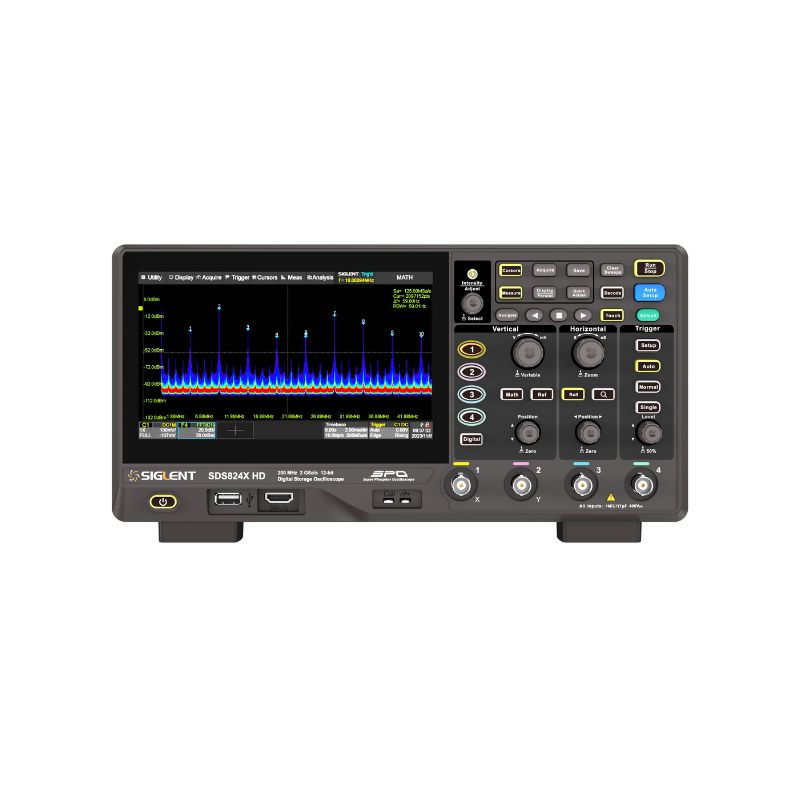

T&M

即納ストア

T&M

即納ストア