NMOSとPMOSを重ねたトランジスタ構造は、CFET (Complementary FET、相補型FET)と呼ばれ、次世代の半導体微細化技術の究極的な構造として注目されています。

CFETは、従来のCMOS(相補型MOS)回路で横に並べて配置されていたN型トランジスタ(NMOS)とP型トランジスタ(PMOS)を、垂直方向に上下に積層した革新的な構造です。

CFETの構造と原理

CFETは、主に既存のGAAFET(Gate-All-Around FET、全周ゲート型FET)またはナノシートFETを基盤として、さらに発展させたものです。

-

積層構造:

-

NMOSとPMOSを垂直に重ねます(例:下層にPMOS、上層にNMOS)。

-

それぞれのトランジスタは、ナノシートやナノワイヤなどの全周ゲート構造(GAA)をとることが多いです。

-

-

CMOS回路の実現:

-

CMOS回路は、NMOSとPMOSをペアにして構成することで、スイッチの切り替え時にのみ電流が流れ、待機時の電力消費を大幅に抑えます。

-

CFETでは、このペアを垂直に積層することで、1つのデバイスの設置面積でCMOSインバータ(基本回路)を実現します。

-

-

モノリシック/シーケンシャル:

-

製造方法として、上下のトランジスタを一体的に形成するモノリシックCFETと、下のトランジスタの上に次のトランジスタを順に形成するシーケンシャルCFETが研究されています。

-

CFETの主な利点

CFETの最大の目的は、ムーアの法則をさらに延長し、トランジスタの集積度と性能を限界まで高めることです。

1. 圧倒的な面積効率(集積度向上)

-

従来のFET構造では、CMOSを構成するNMOSとPMOSの間には、ある程度の**間隔(スペース)**が必要でした。

-

CFETでは、このN型とP型のトランジスタを垂直に重ねることで、横方向の占有面積を約半分に削減できます。これにより、チップ上のトランジスタ密度が劇的に向上します。

2. 性能と消費電力の改善

-

トランジスタ間の距離が短くなるため、配線長が短くなり、寄生容量(意図せず発生する電気容量)が低減します。

-

結果として、動作速度の向上(高性能化)と、エネルギー効率の向上(低消費電力化)が期待されます。

3. 次世代プロセスへの対応

CFETは、現在主流となっているナノシートFETやForksheet FETのさらに次の世代、具体的には1nm台のプロセスノードで採用されることが有力視されている技術です。

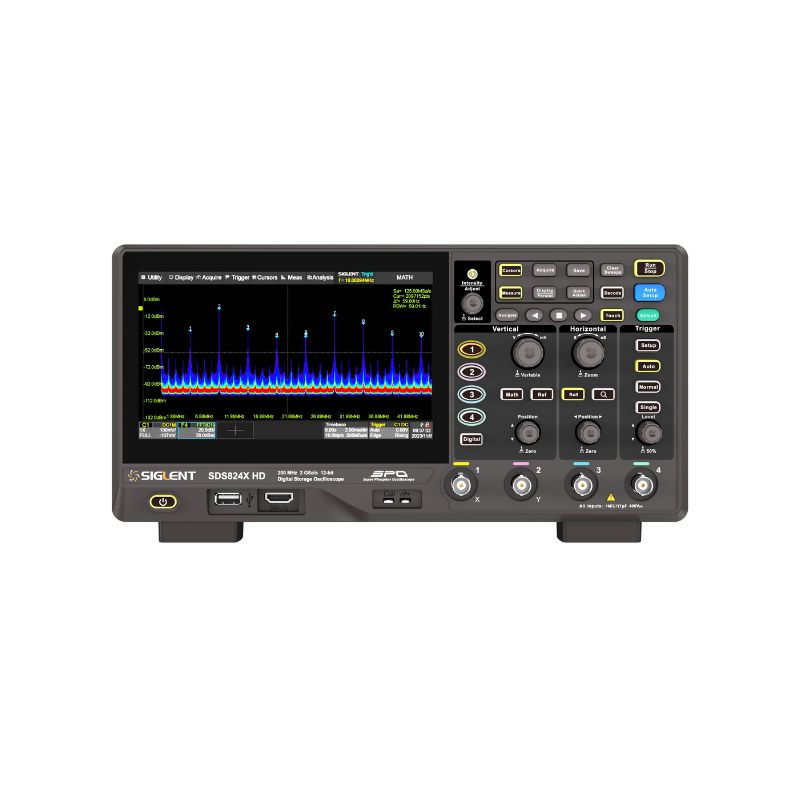

T&M

即納ストア

T&M

即納ストア